3.2 Parallel Fault Simulation

As discussed in the last section, serial fault simulation processes one fault in one iteration. Parallel fault simulation, as the name suggests can processes more than one fault in one pass of the circuit simulation. Parallel fault simulation uses bit-parallelism of a computer. For example, in a 16-bit computer (where a word comprises 16 bits) a logical operation (AND, OR etc.) involving two words performs parallel operations on all respective pairs of 16-bits. This allows a parallel simulation of 16 circuits with same structure (gates and connectivity), but different signal values.

In a parallel fault simulator, each net of the circuit is assigned a 1-dimensional array of width w , where w is the word size of the computer where simulation is being performed. Each bit of the array for a net I say, corresponds to signal at I for a condition (normal or fault at some point) in the circuit. Generally, the first bit is for normal condition and the other bits correspond to w – 1 stuck at faults at various locations of the circuit.

In case of parallel simulation, input lines for any gate comprise binary words of length w (instead of single bits) and output is also a binary word of length w. The output word is determined by simple logical operation (corresponding to the gate) on the individual bits of the input words. Figure 9 explains this concept by example of an AND gate and an OR gate where w is taken to be 3. In the example, in gate G1, input word at I1 is 110 and that in I2 is 010. Output word 010 is obtained by bit wise ANDing of the input words at I1 and I2; this is similar to simulating the gate for three input patterns at a time namely, (i) I1=1, I2=0 (ii) I1=1, I2=1 and (iii) I1=0, I2=0.

Figure 9. Example of parallel simulation

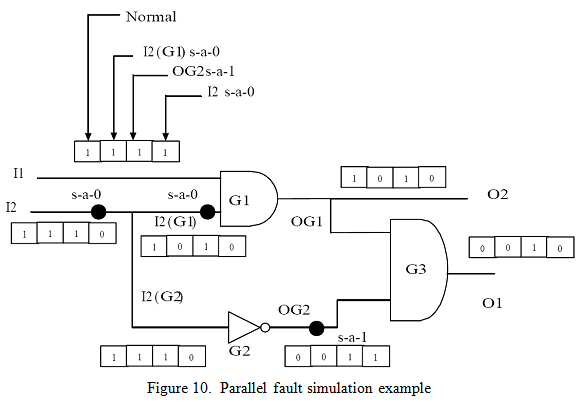

Now we will discuss how parallel fault simulation can determine status of w-1 faults being covered or not given a random test pattern. Let us consider the same circuit used in Figure 7 for explanation of serial fault simulation. We consider the same three faults namely, (i) s-a-0 at I2, (ii) s-a-0 at I2(G1), (iii) s-a-1 at OG2 and the random pattern I1=1, I2=1. It will be shown how parallel fault simulation can discover coverage for these three faults for the input pattern I1=1, I2=1 in one iteration. As there are three faults we need w=4. Figure 10 illustrates parallel fault simulation for this example.