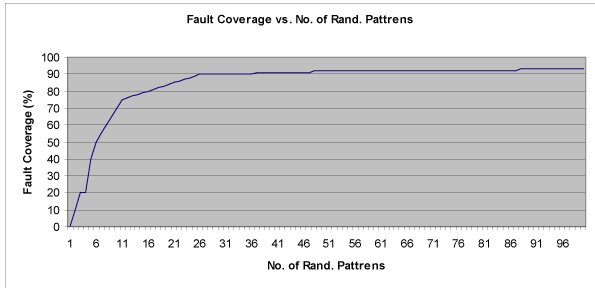

Figure 2. Typical scenario for fault coverage versus random patterns

From the discussion we conclude that TPG can be done in two phases

- Use random patters, till a newly added pattern detects a reasonable number of new faults

- For the remaining faults, apply “sensitize-propagate-justify” approach

Also, it may be noted that determining the output of the circuit for a given input (with and without fault) is the key step for “random pattern based TPG”. In this lecture we will first algorithms for computing the output of a circuit given an input; this is called circuit simulation . Following that we will discuss efficient techniques to determine faults covered by random patterns, called fault simulation .

.2. Circuit Simulation

What is circuit simulation?

The imitative representation of the functioning of circuits by means of another alternative, a computer program say, is called simulation. In digital laboratory (of undergraduate courses), “breadboards” were used to design systems using discrete chips. The same system can be developed using a single VLSI chip. However, we still prefer to do the breadboard design first, as the proof of concept. Breadboard based designs are used as proof of concept because we can predict the result of building the VLSI chip without actually building it. Further, errors can be easily rectified in the breadboard. So we may say that breadboard is a “hardware based” simulation of the VLSI chip. Breadboard has been used over decades for pre-design validation, however, is too cumbersome for large designs. Today, breadboards have been replaced by computer simulations. A circuit is converted into a computer program which generates the output given the input. Obviously, changes due to errors discovered are simple (than breadboard) as one needs to change only a computer program. There are several schemes of circuit simulation [1,2,3], and here we will see the ones related to fault simulation for the stuck-at fault model.