3.3 Deductive Fault Simulation

Form the discussion in the last section it can be noted that parallel fault simulation can speed up the procedure only by a factor that is dependent on the bit width of the computer being used. In this section we will discuss about deductive fault simulation, a procedure which can determine in a single iteration, detectability/undetectability about all faults by a given random pattern. In the deductive method, first the fault-free circuit is simulated by a random pattern and all the nets are assigned the corresponding signal values. “Deductive”, as the name suggests, all faults detectable at the nets are determined using the structure of the circuit and the signal values of the nets. Since the circuit structure remains the same for all faulty circuits, all deductions are carried out simultaneously. Thus, a deductive fault simulator processes all faults in a single pass of simulation augmented with the deductive procedures. Once detectability of all the faults for a random pattern is done, the same procedure is repeated for the >> random pattern after eliminating the covered faults.

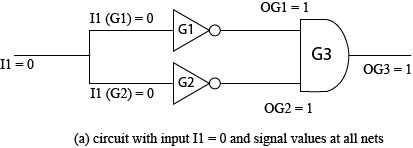

We will explain the procedure by a simple example circuit given in Figure 11.

Figure 11. Example of deductive fault simulation with input I1=0

.....

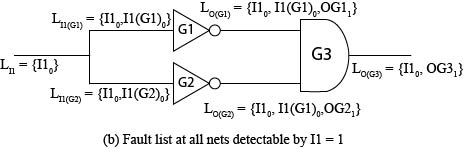

>> we will see the fault deductions at the various nets if I1=1. This situation is illustrated in Figure 12.

Figure 12. Example of deductive fault simulation with input I1=1