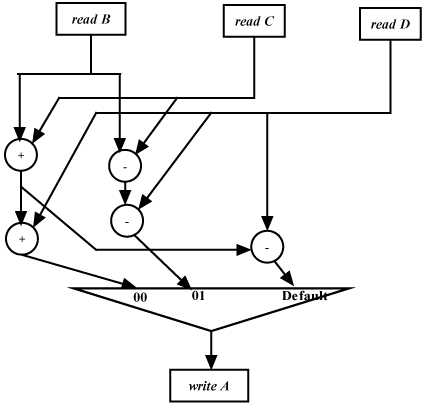

Figure 9. Data flow based CDFG for Verilog code of Figure 8

5. Conclusions

In this lecture is we have stated the concept that for automation, input data is to be represented using appropriate models. In case of HLS, the first step of VLSI design flow, several modeling paradigms exist like CDFG, FSM, FSMD, DeJong's hybrid flow graph, SSIM flow graph etc. In this lecture, we have discussed CDFG framework in details and illustrated with several examples. Following this modeling step, the CDFGs need to transformed so they become more amenable for HLS tasks like scheduling, allocation and binding. The next lecture focuses on transformations of CDFG for HLS.