In the manufacturing steps, we saw that materials have to be removed only in certain places. The process enabling us to define these places is lithography. The complete name is photolithography, but it is also called as lithography or litho in the industry.

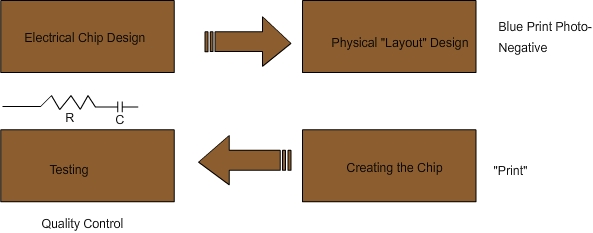

Consider the process flow given in Figure 2.1

Figure 2.1. Overall flow in chip manufacturing process.

Let us assume that the circuit has been designed and the layout is also generated. The layout will be a file in the computer. This information will be used to generate masks. The masks can be thought of as photonegatives. Using these negatives, any number of photos (i.e. chips) can be generated. We will see the details of the layout file, mask making and chip making here.

Layout:

Just like we call the Microsoft word® file as “doc” file and acrobat® portable document format as “pdf” file, these files have certain standard extensions. GDS is one popular format for the layout file.

The transistor locations are called active sites. An IC will have many layers such as active, gate, metal-1 for the first layer of interconnect metal lines etc. Hence, the GDS file of the chip will have information for all the layers. Many parts of the chips can be repetitive. For example, in a memory chip (RAM), the circuit used to store the information is called a bit. The chip will have millions of identical bits where 1’s and 0’s can be stored. All these bits will have identical circuit. It is not necessary to store the layout information of each bit in the GDS file. It is sufficient to store the information of one bit and then refer to it or give a pointer to it in other locations. This way of storing information is called ‘hierarchical’.

We will consider an analogy to understand this. For example, in a small company, there may be 20 operators, 5 supervisors, 2 managers and one managing director. Let us assume that all the persons in a certain designation are paid identical salary. Let us also assume that one supervisor and four operators working under the supervisor are called as “group”. If we want to compute the total salary expense in a month for the company, it is sufficient to know the salary of one operator, one supervisor, one manager and one managing director to calculate it. For this purpose, it will be redundant and a waste of effort to describe the details of the salary of every individual separately. In fact, if we know only the ‘group salary’, and the salary of a manager and the managing director, it is sufficient to calculate the total monthly salary expense. We do not even need to know the salary of an individual operator. On the other hand, if an individual operator falls ill and another operator does an extra shift, we need to know the identity of individual operators to calculate the salary for that month correctly. Thus, there are some occasions where individual level information is not necessary and group level information is sufficient; there are also occasions where individual level information is necessary.

Similarly, a small group of transistors can be stored as ‘circuit 1’ and another different group of transistors may be grouped as ‘circuit 2’ and yet another as circuit 3. A combination of circuit 1 and 2 may be grouped as ‘higher level 1’ By this arrangement, the layout file size will be significantly reduced, for most of the designs. Even with this reduction, the typical layout file sizes are a few gigabytes. To describe the overall layout, hierarchical format is preferred. In order to perform complicated tasks such as optical proximity correction (OPC), which will be described in the later section, the full detailed format is necessary. The complete detailed layout is sometimes called as “flat” file, in contrast to the “hierarchical” file.

Mask:

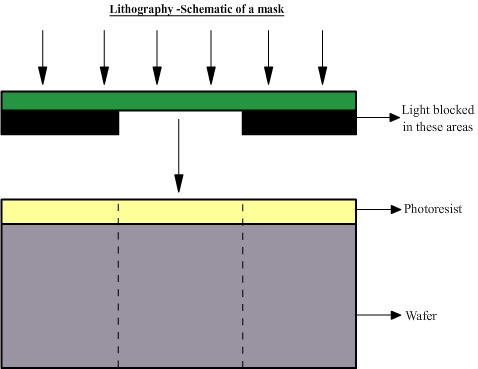

The layout file is then placed in a mask writer machine. What is a mask? It is like a stencil, where a flat plate is taken and holes of desired shapes or letters are cut in it. If we place the stencil on top a paper and paint it, the shapes or letters will come nicely and this can be done over any number of papers to get identical results. Instead of cutting holes, the mask has transparent areas which allow light and certain areas which block the light. A schematic of the mask is given in Figure 2.2

Figure 2.2 Schematic of a mask with wafer and photo resist

Based on the information in the layout file, a mask will be created for each layer. For example, active sites will have a mask and the gate will have a different mask. The mask making is done as follows: A glass plate with chromium deposited on top of it is used as the base. On top of the chromium, a chemical sensitive to electrons is coated. This is called ‘resist’. Then a beam of electrons is directed towards areas (rectangles) that should be open. Electron beam scans the whole mask and whenever the mask is supposed to be ‘open’, the electron beam is ON. Whenever the mask is supposed to block the light, the electron beam will be off. This way, the whole mask is written point by point or ‘pixel by pixel’. Mask making is a tedious work which takes about a day. If there is any small error in the mask, it can be ‘repaired’, but large errors will lead to remaking the whole mask. Masks with very small features are very expensive and the cost of making them is of the order of a million US dollars (about Rs. 5 crores ). The masks are usually not made in the fabs where the ICs are made. Instead mask making is handled by a different department or even outsourced.

|