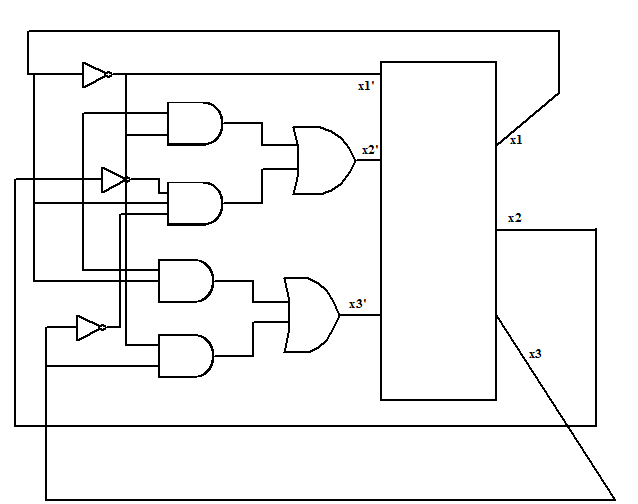

Figure 7. Circuit diagram of MOD-6 counter

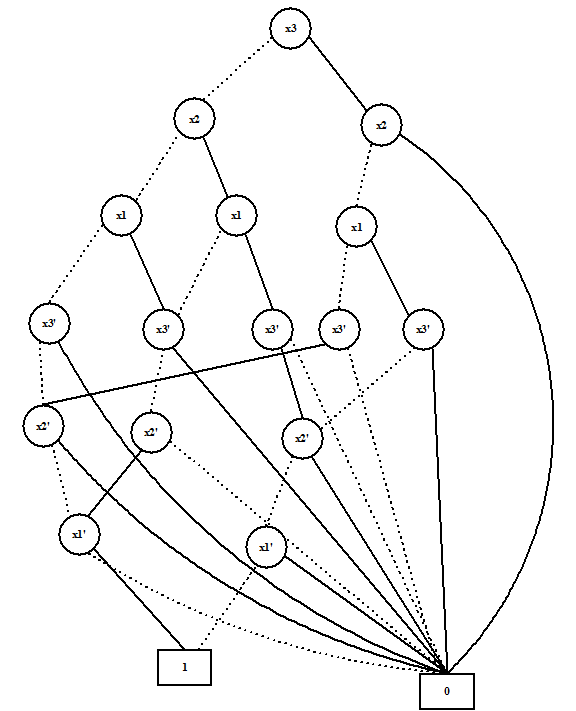

Figure 8. ROBDD [ x 3 , x 2 , x 1 ,x' 3 , x' 2 ,x' 1 ] for MOD-6 Counter

6. Conclusions

In this module we first motivated the use of ROBDD for equivalence checking because of two properties namely, canonicity and non-redundancy. Following that we discussed in detail the construction procedure of ROBDDs and modelling of combinational and sequential circuits using them. However, as discussed in Module-1 (design part of the course), initially the design intents are specified in high level like “whenever a request is made, access to a resource is eventually granted, but it is never granted to two requestors simultaneously”. For equivalence checking of high level specifications with implementation, model checking using temporal logic is widely accepted. In the next module we will introduce temporal logic.