| Contd... |

| Due to the symmetry of the CMOS circuit the rise time can be similarly obtained as; |

|

| For equally sized n and p transistors (where βn=2βp) tf=tr |

| Thus the fall time is faster than the rise time primarily due to different carrier mobilites

associated with the p and n devices thus if we want tf=tr we need to make βn/βp =1.

This implies that the channel width for the p-device must be increased to approximately 2 to 3

times that of the n-device. |

| The propagation delays if calculated as indicated before turn out to be, |

|

|

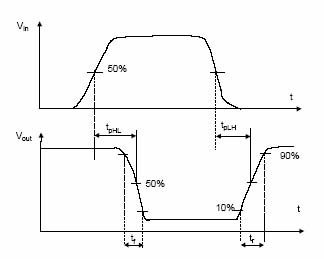

If we consider the rise time and fall time of the input signal as well, as shown in the fig 16.35 we have,

These are the rms values for the propagation delays. |

| Figure 16.35: Rise and Fall time graph of Output w.r.t Input |

|

| |