Electromigration: When current is passing through a conductor, the electrons move from one end to the other end. They transfer some of their momentum to the metal atoms and gradually the metal atoms also move. This is called electromigration. This phenomenon is not of much importance when the current densities are low. In IC chip the current densities are very high and electromigration can cause failure of a circuit.

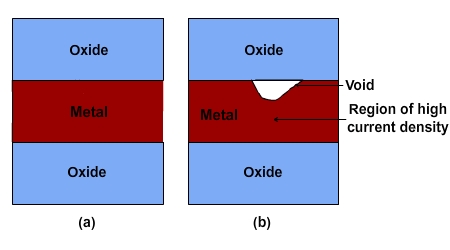

Fig 9.4 Schematic of electromigration causing failure. (a) Early stages. Wire occupies the entire space and the current goes through the metal. Current density is moderate (b) Void formation leads to decreased area available for conduction and increased current density. Acceleration of failure.

In the beginning, the metal would fill the space between the insulators and the current density would be at a certain level (Fig 9.4a). If sufficient atoms move due to electromigration, then a small void will form. Now the all current has to go through the metal and hence near the void region, the current density will increase. The electrical resistance of the metal line is also higher now, because the electrical resistance is inversely proportional to the cross sectional area. This results in larger heat release and hence higher local temperature. At higher temperatures, the metal atom diffusivity is higher, which makes it easier to ‘push’ the atoms. The increased current density and higher temperature accelerates the formation of voids and finally results in the circuit failure.

The extent of electromigration movement depends on the nature of the material. For example, materials such as copper, tungsten and gold have good electro migration resistance. We must note the difference between electrical resistance and electro migration resistance clearly. Electrical resistance indicates the resistance to movements of electrons. We want good electrical conductors (i.e. low electrical resistance). At the same time, we want materials which have high electro migration resistance.

If the electro migration resistance is poor, then after many hours of operation, the resistance of one or few wires will increase dramatically. It can lead to the failure of the chip. These types of failures, where the chip originally functions well and after few months of operation fails, are called “reliability issues”. This means that the chip appears to be good during testing in the fab, but it is not reliable and after sometime it can fail.

Aluminum has low electromigration resistance. To enhance its electromigration resistance, usually a small amount of Cu is added during the deposition of Al. Similarly, a small amount of Si is also added to Al. This is because Si has the tendency to dissolve into aluminum and the silicon in the insulator (silicon dioxide) may diffuse into aluminum. If the aluminum is already saturated with silicon, then further dissolution of Si in Al will not be possible. Thus, both Si and Cu are added in small quantities (1% for example) in the aluminum lines to minimize silicon dissolution and electromigration, respectively. Tungsten has a good electromigration resistance and hence the vias or contacts made of tungsten are quite immune to this issue.

The average time for failure, which is called MTF or mean time to fail, depends on the current density and the temperature. Usually if the wires are made with large grains, that is large crystals then it will not be easy to break the wire. If the size and the arrangement (that is the orientation of the grains) are good then the electro migration resistance will be high and the chip will not fail easily.

In order to test whether a material or chip will function for a long time without failure, frequently the chip is tested at high temperature. This is called high temperature operation test or HTOT. Sometimes the chip is also tested at a high temperature and high humidity. This is called highly accelerated stress test or HAST. Hence in every batch few chips will be tested using this to understand whether the chips made during those processes are prone to failure in the medium term.

The length of the metal line and the current density passing through that determine the MTF. The minimum value of the product of length and current density (L * j) needed for electromigration to cause catastrophic failure is called Blech product, named after I.A. Blech, who proposed it first. The higher the current density or longer the line, more the chance of failure by electromigration. For a given current density and material choice (Cu or Al), the critical length (minimum length) above which electromigration can cause failure is called Blech length.

Cu metallization – Process integration: Copper has lower electrical resistance and higher electromigration resistance then aluminum. Hence it was introduced as interconnect material in the 1990s. Dry etching of copper was difficult and hence the aluminum process integration scheme could not be used for copper. A new set of processes and sequence was needed. The following describes the process integration scheme of copper metallization.

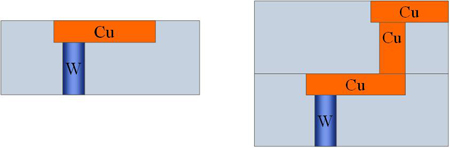

(a) (b)

Fig 9.5. Schematic of chip in BEOL , with Cu line (a) after M1 layer (b) after fabrication of via12 and M2 layer

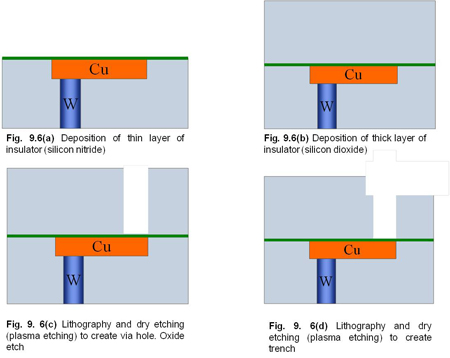

At first, a thin layer of silicon nitride is deposited on top of copper, by LPCVD as shown in Fig 9.6 a. Next, a thick layer of silicon dioxide is deposited on top (Fig. 9.6 b). Both the silicon nitride and silicon dioxide are insulators. In the next step, using lithography and dry etching, holes for the vias are created (Fig 9.6 c). In this process, the etching ‘stops on nitride’. i.e. only the oxide layer is removed but the nitride layer is not removed. The etching chemicals and process conditions are chosen such that only the oxide will etch.

Then, again using lithography and dry etching, trenches for metal lines are made (Fig. 9.6 d). This is called as ‘blind etch’ because the etch does not stop at another material. The etching time is controlled so that the expected depth (with some variation) will be created.

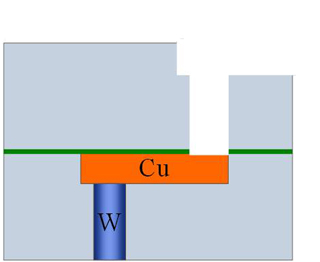

After this step, thin layer of the silicon nitride, inside the via hole, is removed using dry etching using suitable combination of chemicals and plasma (Fig. 9.6 e). During this etch, a slight damage to Cu lying below may occur. However, since the nitride layer is thin, the etch time will be very short and the damage is also limited. If the nitride layer were not present and only oxide were used as insulator, the potential damage to Cu line would be severe.

Fig. 9. 6(e), Dry etching (plasma etching) to remove nitride at the bottom layer

Subsequently, a thin layer of barrier (Ta/TaN, and in some cases, an additional layer of Ru) is deposited (Fig. 9.6 f). This is needed to prevent the diffusion of Cu through the silicon dioxide insulator. Then, another thin layer of Cu is deposited using CVD method (Fig. 9.6 g). This is needed to obtain a layer of at least moderate electrical conductivity for the next step.

Fig. 9.6(f), Ta/TaN deposition by PVD

Fig. 9. 6(g) Cu seed layer deposition by CVD (or PVD)

After the seed layer is deposited, a thick Cu layer is deposited using electrochemical deposition (Fig 9.6 h). The Cu formed has larger crystals, lower electrical resistance and higher electromigration resistance compared to Cu deposited by other methods such as PVD or CVD. The Cu can not be deposited only inside the vias and trenches. Hence it is deposited throughout the wafer surface. Then in the next step, the excess Cu is removed using CMP (Fig. 9. 6 i)

Fig. 9. 6(h) Cu deposition by electrochemical deposition

Fig. 9. 6(i) Removal of excess Cu by first stage of CMP- (Main Cu CMP)

Fig. 9. 6(j) Ta/TaN (barrier layer) removal by 2nd stage of CMP (Barrier CMP)

The removal is done in two steps. In the first step, only the Cu is removed. The barrier and the insulator are not removed (Fig. 9.6 i). In the second step or 2nd stage of the CMP, a different slurry is used and the barrier metal is also removed in the unwanted places (Fig. 9.6 j). Subsequently, the Cu is annealed so that the crystal size increases.

This scheme of intergration is called “via first” integration because via holes are made before trenches here. In another process sequence, the trenches can be made first and the vias can be made afterwards (i.e. the processes in Fig. 9.6 c and Fig. 9.6 d can be done in reverse order) and that scheme is called “trench first” integration. Most fabs use the via first scheme for copper metallization.

Summary: Process integration denotes combining various processes to obtain the desired structure, to obtain a functioning chip, in a robust fashion. In the modern chips, the BEOL part plays a significant role in determining the yield as well as the speed of the chip. Electromigration is the movement of metal atoms due to the movement of electrons. It can cause failures at the later stage of chip operation and hence is a reliability issue. If the metal lines are long, and/ or if large current densities are used, then the chances of failure by electromigration is high. It is desirable to have high electromigration resistance and low electrical resistance. Aluminum has more electrical resistance than Cu and less electromigration resistance than Cu. However, it can be etching using plasma and a process sequence using tungsten vias and aluminum metal lines was used to make interconnects. With the introduction of CMP, it is possible to make Cu vias and Cu metal lines on chips, and the different process sequence needed to obtain Cu interconnects was discussed. |