| |

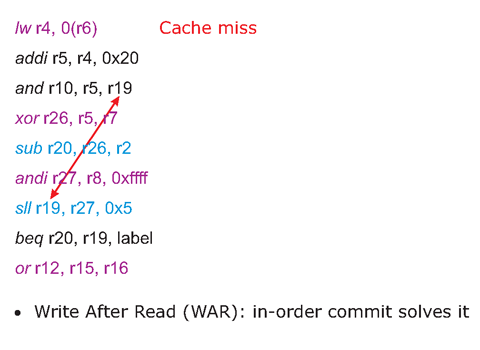

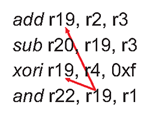

WAR hazard

Modified bypass

- An executing instruction must broadcast results to the issue queue

- Waiting instructions compare their source register numbers with the destination register number of the bypassed value

- Also, now it needs to make sure that it is consuming the right value in program order to avoid WAR

- Need to tag every instruction with its last producer

- Can we simplify this?

WAR and WAW

- These are really false dependencies

- Arises due to register allocation by the compiler

- Thus far we have assumed that ROB has space to hold the destination values: needs wide ROB entries

- These values are written back to the register file when the instructions retire or commit in-order from ROB

- Also, bypass becomes complicated

- Better way to solve it: rename the destination registers

|

| |

| |

| |

| |

| |

| |

| |

| |

| |

| |

| |

| |

| |

| |

|

|

|

|