| |

Instruction selection

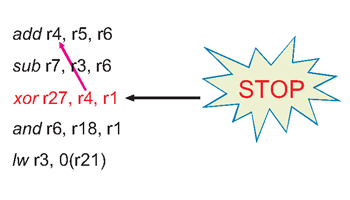

- Simplest possible design

- Issue the instructions sequentially (in-order)

- Scan the issue queue, stop as soon as you come to an instruction dependent on one already issued

- Cannot issue the last two even though they are independent of the first two: in-order completion is a must for precise exception support

In-order multi-issue

- Complexity of selection logic

- Need to check for RAW and WAW

- Comparisons for RAW: N(N-1) where N is the issue width

- Comparisons for WAW: N(N-1)/2

- 18 comparators for 4-issue

- Still need to make sure instructions write back in-order to support precise exception

- As instructions issue, they are removed from the issue queue and put in a re-order buffer (also called active list in MIPS processors) [Isn’t WAW check sufficient?]

- Instructions write back or retire in-order from re-order buffer (ROB)

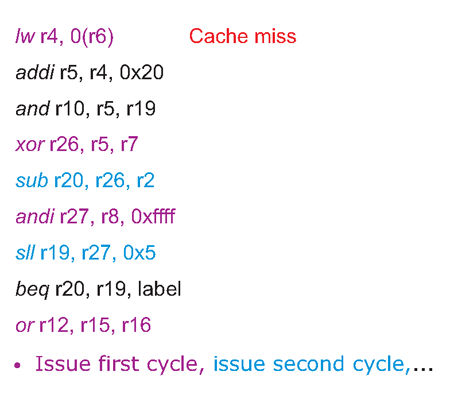

Out-of-order issue

- Taking the parallelism to a new dimension

- Central to all modern microprocessors

- Scan the issue queue completely, select independent instructions and issue as many as possible limited only by the number of functional units

- Need more comparators

- Able to extract more ILP: CPI goes down further

- Possible to overlap the latency of mult/div, load/store with execution of other independent instructions

|

| |

| |

| |

| |

| |

| |

| |

| |

| |

| |

| |

| |

| |

| |

|

|

|

|