| |

Register renaming

- Registers visible to the compiler

- Logical or architectural registers

- Normally 32 in number for RISC and is fixed by the ISA

- Physical registers inside the processor

- The destination logical register of every instruction is renamed to a physical register number

- The dependencies are tracked based on physical registers

- MIPS R10000 has 32 logical and 64 physical regs

- Intel Pentium 4 has 8 logical and 128 physical regs

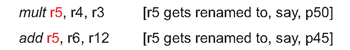

- Now it is safe to issue them in parallel: they are really independent (compiler introduced WAW)

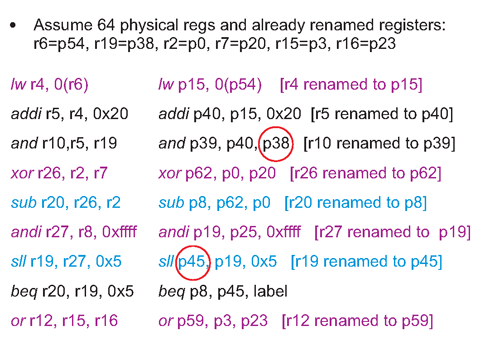

- Register renaming maintains a map table that records logical register to physical register map

- After an instruction is decoded, its logical register numbers are available

- The renamer looks up the map table to find mapping for the logical source regs of this instruction, assigns a free physical register to the destination logical reg, and records the new mapping

- If the renamer runs out of physical registers, the pipeline stalls until at least one register is available

- When do you free a physical register?

- Suppose a physical register P is mapped to a logical register L which is the destination of instruction I

- It is safe to free P only when the next producer of L retires (Why not earlier?)

- More physical registers

- more in-flight instructions

- possibility of more parallelism

- But cannot make the register file very big

- Takes time to access

- Burns power

|

| |

| |

| |

| |

| |

| |

| |

| |

| |

| |

| |

| |

| |

| |

|

|

|

|