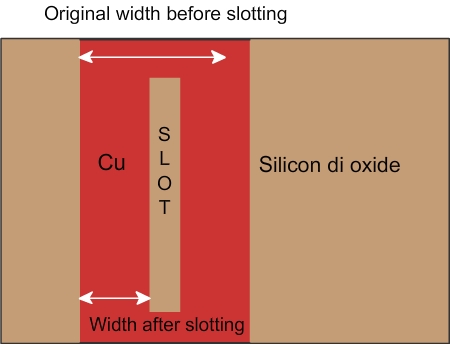

Slotting and dummy fill: In order to provide fairly uniform aerial density, two features called “slotting” and “dummy fill” are used. Consider a wide copper line, shown in the top view (fig.4.19a). The aerial density can be reduced by decreasing the line width, but this will increase the electrical resistance. Instead, the line is made even wider, but islands of oxide are introduced in the line (fig 4.19b). This is also called “introduction of slots” or “slotting”. This will prevent excessive dishing during CMP.

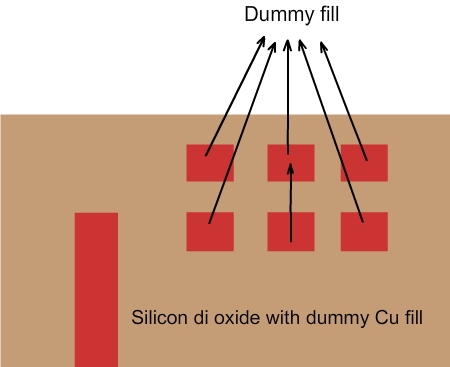

Similarly, if an area does not contain copper at all, because there are no connections needed in that location, it will have only oxide (fig. 4.20b)

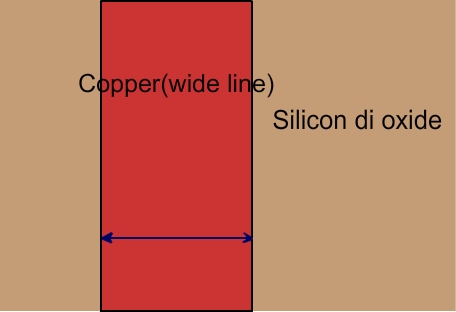

Figure 4.19 a. Top view of a wide line before slotting

Figure 4.20. b. Top view of the same line after slotting. Note that the new line is wider than the original line in some places, but in most places, the width is less after introduction of slot

Figure 4.20 a. Top view of an area before dummy fill.

Figure 4.20 b. Top view of an area after dummy fill.

In these cases, a few islands of copper are added in the layout. Note that these copper lines will not connect to any other line and do not serve any purpose in the final chip. They are introduced only to ensure that the CMP process will planarized the chip properly. This is similar to adding protective diodes connected to aluminum islands to avoid ESD during dry etch.

If the aerial density varies a lot in the chip, the CMP process will not be able to planarized the surface effectively. Slotting will reduce the density from very high value to an acceptable value. Dummy fill will increase the density from very low value to an acceptable value. Together, these two tricks are used to convert the layout to a process friendly form.

Copper interconnects have become part of the IC manufacturing only after copper CMP was introduced. Before that, although the scientists attempted using dry or wet etch to create copper lines, they were not successful in a commercial scale. In the early 1990s IBM engineers created chips with copper lines. Since CMP enabled the introduction of copper wires, it is called enabling technology. The fact that many small devices like cell phones and laptops can run on a battery for a long time is due to the fact that copper wires are used in the ICs.

CMP also plays a key role in electrically isolating transistors. A technique called shallow trench isolation (STI) is used to keep the transistors electrically isolated. While silica abrasives are used for Cu CMP slurries, silica or ceria abrasives are used for STI CMP slurries. The details of STI and the role of CMP process in STI is described in the front end of line (FEOL) section. In the next section we will see the three techniques used to modify the material viz. 1. Ion implantation, 2. Diffusion and 3. Oxidation. |