Course abstract

This course discussed how a C code can be automatically translated into register transfer level (RTL) design using high-level synthesis (HLS). HLS is an active domain of research in recent times in the domain of electronic Design Automation (EDA) of VLSI. This course will help the student to (i) understand the overall HLS flow, (ii) how a C-code will be converted to its equivalent hardware, (iii) how to write c-code for efficient hardware generation and (iv) how the common software compiler optimization can help to improve the circuit performance. Also, advanced topics like HLS for FPGA targets, HLS for Security, optimizations at RTL level and verification challenges of HLS will be covered. This course will help the student to take up research in the domain of HLS. Also, this course will help the student to become proficient for EDA industries.

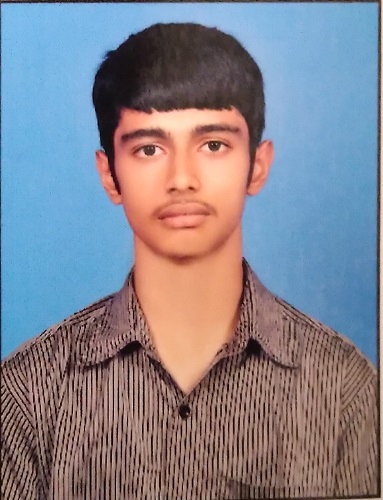

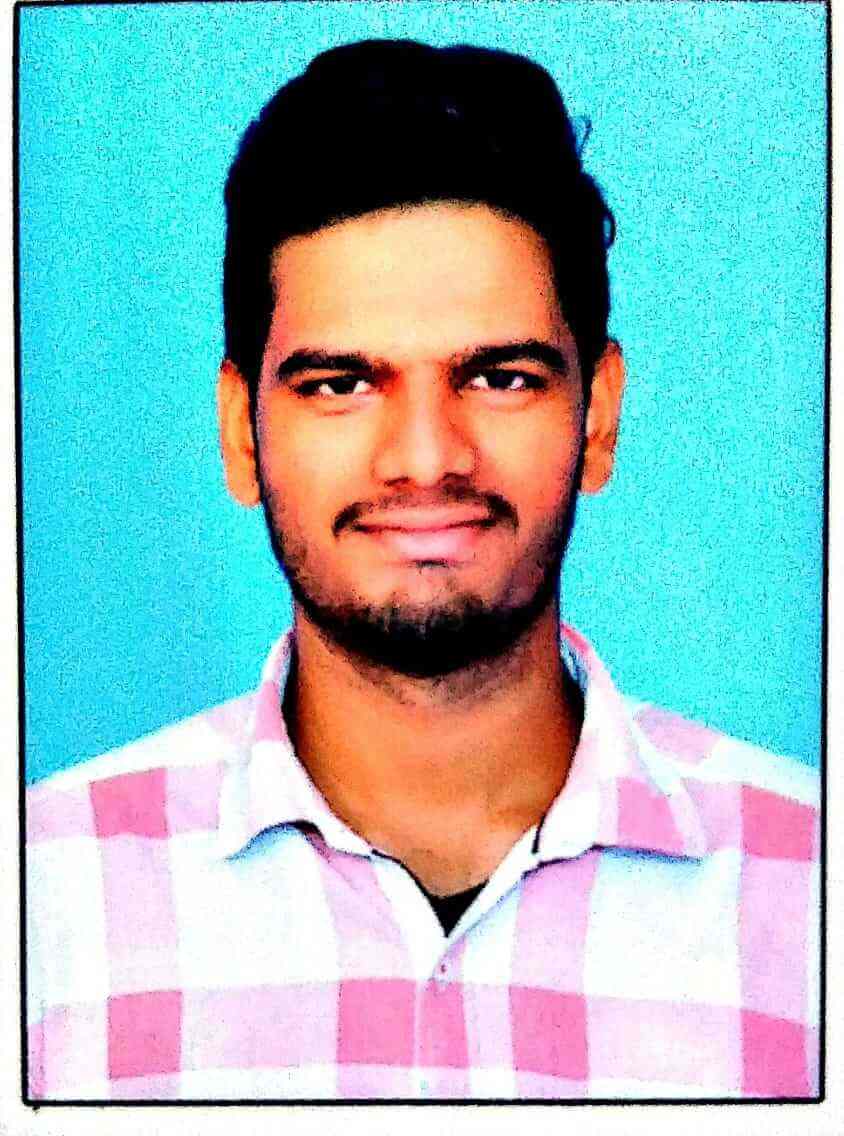

Course Instructor

Prof. Chandan Karfa

Dr. Chandan Karfa is an Assistant Professor in the Dept. of CSE, IIT Guwahati since 2016. He has over fifteen years of teaching and research experience. He has so far taught many courses in UG and PG level in IIT Guwahati. He has worked for five years as Senior R&D engineer in EDA Industry in the domain of High-level Synthesis and Logic Synthesis. He has worked as visiting researcher at New York University, May - July 2019. His research interests include High-level Synthesis, CAD for VLSI, Hardware Security and Formal Verification. He has published more than thirty five research papers in reputed international journals and conferences. He has graduated one PhD student and guided twelve MTech and twenty two BTech projects. He is an IEEE Senior member. He was recently awarded the Qualcomm Faculty Award 2021 which recognizes distinguished faculty research that inspires students and sparks new approaches in key technology areas.More info

Teaching Assistant(s)

No teaching assistant data available for this course yetCourse Duration : Jul-Oct 2021

View Course

Syllabus

Enrollment : 20-May-2021 to 02-Aug-2021

Exam registration : 17-Jun-2021 to 17-Sep-2021

Exam Date : 24-Oct-2021

Enrolled

4668

Registered

143

Certificate Eligible

87

Certified Category Count

Gold

8

Silver

29

Elite

30

Successfully completed

20

Participation

31

Legend

AVERAGE ASSIGNMENT SCORE >=10/25 AND EXAM SCORE >= 30/75 AND FINAL SCORE >=40BASED ON THE FINAL SCORE, Certificate criteria will be as below:

>=90 - Elite + Gold

75-89 -Elite + Silver

>=60 - Elite

40-59 - Successfully Completed

Final Score Calculation Logic

- Assignment Score = Average of best 8 out of 12 assignments.

- Final Score(Score on Certificate)= 75% of Exam Score + 25% of Assignment Score

Enrollment Statistics

Total Enrollment: 4668

Registration Statistics

Total Registration : 143

Assignment Statistics

Exam score

Final score

.jpg)

.jpg)

.jpg)

.jpg)