Courses » VLSI Design Verification and test

reviewer1@nptel.iitm.ac.in ▼

Announcements

Course

Ask a Question

**Progress**

Mentor

# **Unit 13 - Fault Simulation and Testability Measures**

#### Week 10 Assignment Course outline The due date for submitting this assignment has passed. Due on 2016-10-01, 23:58 IST. How to access the portal? Submitted assignment Introduction and Overview of VLSI Design 1) The procedure to generate a test input for a given a fault is called \_ 1 point Scheduling in High- Test Procedure Generation **Level Synthesis** Test Pattern Generation Test Parameter Generation **Resource Sharing** and Binding in HLS None No, the answer is incorrect. Logic Synthesis Score: 0 **Physical Design Accepted Answers:** Test Pattern Generation Introduction to 2) How many broad steps are involved to generate a test pattern? 1 point Verification Techniques O Two Three Syntax and semantics of CTL, Four Equivalences Not fixed, depends on circuit between CTL formulas and No, the answer is incorrect. Introduction to Model Score: 0 Checking **Accepted Answers: CTL Model checking** Three Algorithms and Introduction to 3) How many choices are there to sensitize the s-a-1 fault at OG1 (output of Gate 1) in Figure shown below? 1 point **Binary Decision** Diagrams I1 = 012 = 1**Binary Decision** 13 = 1G1 Diagram and I4 = 1Symbolic model checking 1 if fault 16 = 10 if no fault 17 - 1Introduction to ${\tt IS}\!=\!1$ 0 G2 **Digital Testing** 19 = 1**Fault Simulation and Testability Measures** Fault Simulation I Fault Simulation II I21=1-122 = 1 Fault Simulation III 123=1 124 = 1 Testability Measures (SCOAP) Quiz: Week 10 Assignment Combinational **Circuit Test Pattern** Generation $^{\circ}$ 2<sup>5</sup>-1 9 5<sup>2</sup>-1 **Sequential Circuit Testing and Scan** 2<sup>5</sup>+1 Chains

VLSI Design Verification and test - - Unit 13 - Fault Simulation and Testability Measures

Built In Self Test (BIST)

| ○ 5 <sup>2</sup> +1                                                                                                                                                                              |       |

|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------|

| No, the answer is incorrect. Score: 0                                                                                                                                                            |       |

| Accepted Answers:                                                                                                                                                                                |       |

| 2 <sup>5</sup> -1                                                                                                                                                                                |       |

| 4) How many inputs patterns are possible to propagate the fault effect to OG6 (output of Gate 6) in Figure referred 1 n Q3?                                                                      | point |

| ○ 1                                                                                                                                                                                              |       |

| © 2<br>© 3                                                                                                                                                                                       |       |

| ○ 3<br>○ 4                                                                                                                                                                                       |       |

| No, the answer is incorrect.                                                                                                                                                                     |       |

| Score: 0                                                                                                                                                                                         |       |

| Accepted Answers:                                                                                                                                                                                |       |

|                                                                                                                                                                                                  | point |

| All 1s                                                                                                                                                                                           |       |

| All 0s     Combination of 0s and 1s                                                                                                                                                              |       |

| O None                                                                                                                                                                                           |       |

| No, the answer is incorrect. Score: 0                                                                                                                                                            |       |

| Accepted Answers: All 1s                                                                                                                                                                         |       |

| 6) Let us take a random input "10001 11111 11111 11111 11111" for the figure referred in Q3. Then the faults detected at OG1 (output of Gate 1) and OG6 (output of Gate 6) are and respectively. | point |

| S-a-1, S-a-1                                                                                                                                                                                     |       |

| S-a-0, S-a-1                                                                                                                                                                                     |       |

| ○ S-a-1, S-a-0<br>○ S-a-0, S-a-0                                                                                                                                                                 |       |

| No, the answer is incorrect. Score: 0                                                                                                                                                            |       |

| Accepted Answers: S-a-1, S-a-1                                                                                                                                                                   |       |

| 7) If some faults are difficult to be detected in a circuit, approach is used to generate test patterns for them. 1                                                                              | point |

| Sensitize-Propagate-Justify                                                                                                                                                                      |       |

| Random                                                                                                                                                                                           |       |

| Manual                                                                                                                                                                                           |       |

| None of the above                                                                                                                                                                                |       |

| No, the answer is incorrect.  Score: 0                                                                                                                                                           |       |

| Accepted Answers: Sensitize-Propagate-Justify                                                                                                                                                    |       |

| 8) Consider an event driven simulation for a circuit shown below for input pattern I1=1, I2=1 and s-a-0 fault in I2. At 1 ime t=0 the event list = {I1=1, I2=1}. What is the activity list?      | point |

|                                                                                                                                                                                                  |       |

| [2=1 G1 ) O2=0                                                                                                                                                                                   |       |

| s-a-0 12(G1)=0 OG1=0                                                                                                                                                                             |       |

| G3                                                                                                                                                                                               |       |

| O1=? Computation not done                                                                                                                                                                        |       |

| 12(G2)=0 $G2$ $OG2=1$                                                                                                                                                                            |       |

| s-a-0 fault in 12 Condition                                                                                                                                                                      |       |

|                                                                                                                                                                                                  |       |

| ○ I2(G1), I2(G2)<br>○ I2(G1), OG2, I2(G2), O2                                                                                                                                                    |       |

| ○ I2(G1), OG2, I2(G2),O2<br>○ I2(G1), O2                                                                                                                                                         |       |

| ○ I2(G1), OG1                                                                                                                                                                                    |       |

### No, the answer is incorrect.

#### Score: 0

Accepted Answers: 12(G1), 12(G2)

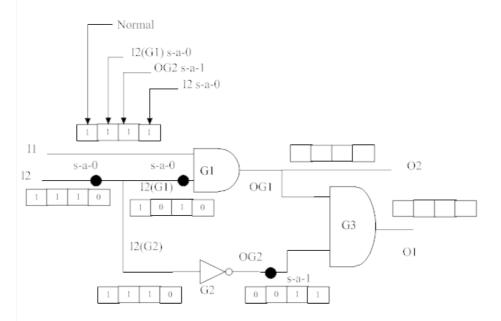

9) Let us consider a circuit shown below that that illustrates parallel fault simulation of a circuit. The simulation uses *1 point* a 4-word array. For the input I1=1 and I2=1 in the circuit, the array at the O2 is \_\_\_\_\_.

- 0 1000

- 0101

- 0 1010

- 0011

### No, the answer is incorrect.

#### Score: 0

#### **Accepted Answers:**

1010

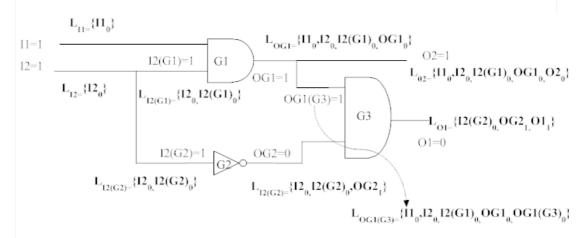

10)By studying the fault list at the primary outputs ( $L_{O1}$  and  $L_{O2}$ ) in the circuit shown below, we find that deductive **1 point** fault simulation discovered \_\_\_\_ faults detectable by pattern I1=1, I2=1.

- 0 4

- 0 8

- **16**

- 32

## No, the answer is incorrect.

Score: 0

### Accepted Answers:

8

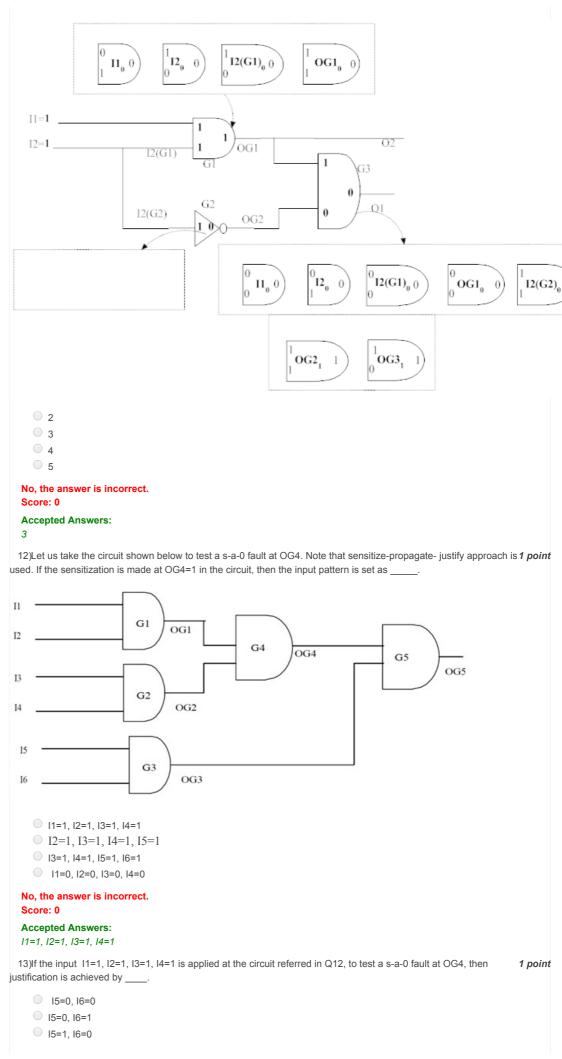

11) Figure shown below illustrates an example of a concurrent fault simulation and the inputs are I1=1 and I2=1. The *1 point* NOT gate G2 can be affected by \_\_\_\_\_ fault(s).

Score: 0

### Accepted Answers:

Min(CCO(b),CCI(b)) + CO(c) + I

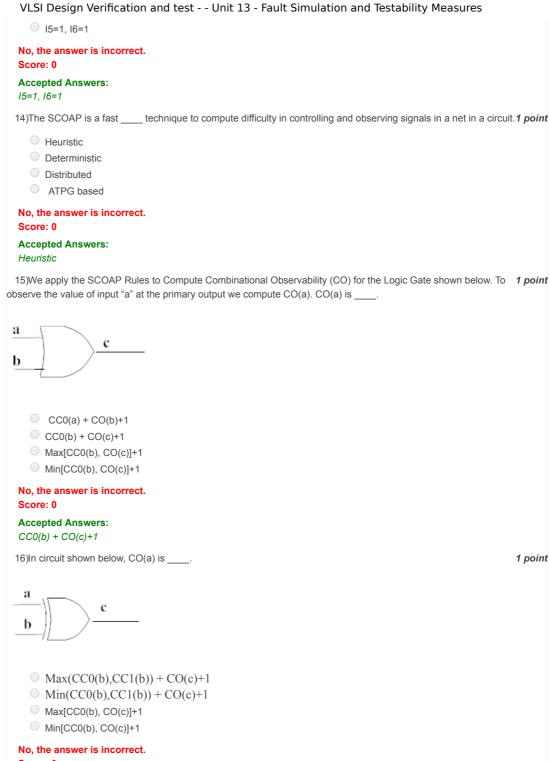

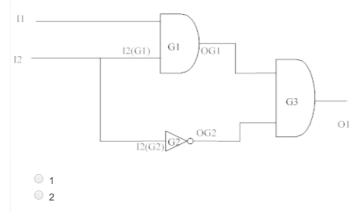

17)Consider the simple circuit shown below for the Combinational Controllability Calculation in the nets. Consider 1 point Level 1 in the circuit, where all the primary input nets (I1,I2) and their fanout branches (I2(G1) and I2(G2)) are directly assigned as 1,1,1,1 respectively. Now, consider Level 2 in in the circuit. The value of the CC0(OG1) is \_\_\_\_\_.

| VLSI Design Verification and test Unit 13 - Fault Simulation and Testability Measures |         |

|---------------------------------------------------------------------------------------|---------|

| O 3                                                                                   |         |

| O 4                                                                                   |         |

| No, the answer is incorrect. Score: 0                                                 |         |

| Accepted Answers:                                                                     |         |

| 18)Consider Level 2 in a circuit referred in Q17. The value of the CC1(OG1) is        | 1 point |

| O 1                                                                                   |         |

| O 2                                                                                   |         |

| ○ <sub>3</sub>                                                                        |         |

| O 4                                                                                   |         |

| No, the answer is incorrect.                                                          |         |

| Score: 0                                                                              |         |

| Accepted Answers:                                                                     |         |

| 3                                                                                     |         |

|                                                                                       |         |

© 2014 NPTEL - Privacy & Terms - Honor Code - FAQs -In association with

Previous Page

A project of

Funded by

Government of India Ministry of Human Resource Development

End