reviewer1@nptel.iitm.ac.in ▼

Courses » Optimization Techniques for Digital VLSI Design

Announcements **Course** Ask a Question Progress Mentor

## Unit 8 - VLSI Testing [Part-2]

| Course outline                                                              | Assignment for Week 6                                                                                                                     |      |

|-----------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------|------|

| How to access the                                                           | The due date for submitting this assignment has passed.  Due on 2018-03-21, 23:59 IS                                                      | T.   |

| portal                                                                      | Submitted assignment                                                                                                                      |      |

| Introduction and<br>High-level<br>Synthesis [Part-1]                        | 1) Compatible bits in test patterns are mainly used for 1 po                                                                              | oint |

| Introduction and<br>High-level<br>Synthesis [Part-2]                        | Test Pattern elimination Test Pattern verification Test Pattern compression All the above                                                 |      |

| RTL Optimizations<br>[Part-1]                                               | No, the answer is incorrect. Score: 0                                                                                                     |      |

| RTL Optimizations<br>[Part-2]                                               | Accepted Answers: Test Pattern compression                                                                                                |      |

| Logic Synthesis<br>and Physical<br>Synthesis                                | Generally speaking, for tester memory optimization, input test vectors are and responses 1 per are  Compressed, compacted                 | oint |

| VLSI Testing [Part-<br>1]                                                   | Compacted, Compressed Compressed, Compressed                                                                                              |      |

| VLSI Testing [Part-<br>2]                                                   | Compacted, Compacted  No, the answer is incorrect.                                                                                        |      |

| Optimization Techniques for ATPG [Part II]                                  | Score: 0  Accepted Answers:  Compressed, compacted                                                                                        |      |

| Optimization Techniques for Design for Testability                          | 3) Test Stimulus Compression based on linear operations are performed by  LFSR  XOR network                                               | oint |

| <ul> <li>High-level fault<br/>modeling and RTL<br/>level Testing</li> </ul> | Neither (a) nor (b)  Both (a) and (b)                                                                                                     |      |

| <ul><li>Quiz : Assignment<br/>for Week 6</li></ul>                          | No, the answer is incorrect. Score: 0                                                                                                     |      |

| <ul><li>Solution of<br/>Assignment 6</li></ul>                              | Accepted Answers: Both (a) and (b)                                                                                                        |      |

| Verification [Part-1]                                                       | 4) Consider the circuit given below. The output is compacted using transition count. What is the value of transition count at the output? | oint |

| Verification [Part-2]                                                       | advision count at the suspect                                                                                                             |      |

|                                                                             | $X_0 = 0011101 \\ X_1 = 0011101 \\ X_2 = 0111010 $ 0001100                                                                                |      |

|           | Optimization lectiniques for Digital VESI Design Offic 0 - VESI Testing [Fait-2]                                                                             |         |

|-----------|--------------------------------------------------------------------------------------------------------------------------------------------------------------|---------|

|           | O 1                                                                                                                                                          |         |

|           | O 2                                                                                                                                                          |         |

|           | <b>3</b>                                                                                                                                                     |         |

|           | O 4                                                                                                                                                          |         |

|           | No, the answer is incorrect.                                                                                                                                 |         |

|           | Score: 0                                                                                                                                                     |         |

|           | Accepted Answers: 2                                                                                                                                          |         |

|           |                                                                                                                                                              |         |

| 5         | i) "If stuck-then fault" model is mainly applicable for                                                                                                      | 1 point |

|           | Gate level testing                                                                                                                                           |         |

|           | RTL testing                                                                                                                                                  |         |

|           | Transistor level testing                                                                                                                                     |         |

|           | Not considered as a fault model                                                                                                                              |         |

|           | No, the answer is incorrect.                                                                                                                                 |         |

|           | Score: 0                                                                                                                                                     |         |

|           | Accepted Answers:  RTL testing                                                                                                                               |         |

|           | ) Huffman compression is a code based compression method, which can be applied on test patterns. nich are true about Huffman compression method?             | 1 point |

|           | High frequency pattern is given lower width.                                                                                                                 |         |

| i.        | High frequency pattern is given higher width.                                                                                                                |         |

| ii.<br>v. | Root corresponds to the lowest frequency pattern.  Root corresponds to the highest frequency pattern.                                                        |         |

| ۷.        |                                                                                                                                                              |         |

|           | ii and iii are true. i and iii are true.                                                                                                                     |         |

|           | Only iii is true.                                                                                                                                            |         |

|           | i and iv are true.                                                                                                                                           |         |

|           | No, the answer is incorrect.                                                                                                                                 |         |

|           | Score: 0                                                                                                                                                     |         |

|           | Accepted Answers:                                                                                                                                            |         |

|           | i and iv are true.                                                                                                                                           |         |

| 7         | Select the false statements about scan chain.                                                                                                                | 1 point |

|           | Parallel scan can reduce test clock cycles with increase in number of I/Os.                                                                                  |         |

| i.<br>ii. | Parallel scan increases test clock cycles but reduces the number of I/Os.  If a FF if it is difficult to control or depth is high it should be scan enabled. |         |

| v.        | Scan chain increases no of multiplexers but reduces testing complexity.                                                                                      |         |

|           | ii and iii are false.                                                                                                                                        |         |

|           | Only ii is false.                                                                                                                                            |         |

|           | iii and iv are false.                                                                                                                                        |         |

|           | Only i is false.                                                                                                                                             |         |

|           | No, the answer is incorrect. Score: 0                                                                                                                        |         |

|           | Accepted Answers:  Only ii is false.                                                                                                                         |         |

| 8         | Select the false statement about High level fault modeling and RTL based testing.                                                                            | 1 point |

|           | High level fault modeling improves test coverage and reliability.                                                                                            |         |

|           | With help of High level fault models, computational complexity of ATPG is addressed.                                                                         |         |

|           | High level fault modeling and RTL based testing are better suited for large circuits like NoC.                                                               |         |

|           | There exists good co-relation between high level fault models and gate level fault models.                                                                   |         |

|           | No, the answer is incorrect.<br>Score: 0                                                                                                                     |         |

|           | Accepted Answers: High level fault modeling improves test coverage and reliability.                                                                          |         |

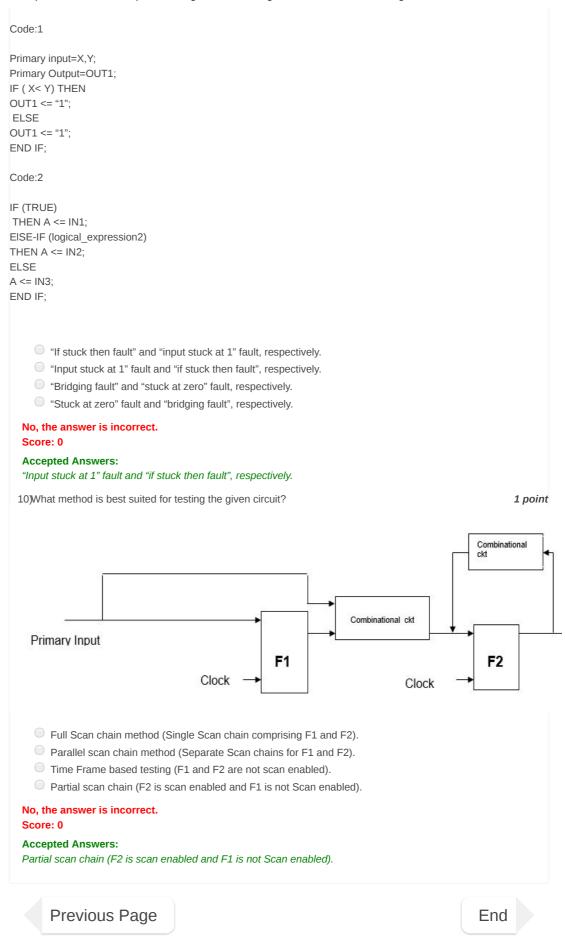

| 9         | ) What kind of fault is represented by the following high level fault model code segments?                                                                   | 1 point |

|           |                                                                                                                                                              |         |

© 2014 NPTEL - Privacy & Terms - Honor Code - FAQs -

A project of

In association with

Funded by

Government of India Ministry of Human Resource Development Powered by