# NPTEL

reviewer1@nptel.iitm.ac.in ▼

## Courses » Optimization Techniques for Digital VLSI Design

Announcements Course Ask a Question Progress Mentor

# Unit 6 - Logic Synthesis and Physical Synthesis

| Course outline                                               | Assignment for Week 4                                                                                                                                                                                                                                                          |         |

|--------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------|

|                                                              | The due date for submitting this assignment has passed. Due on 2018-03-07, 23:                                                                                                                                                                                                 | 59 IST. |

| How to access<br>the portal                                  | Submitted assignment                                                                                                                                                                                                                                                           |         |

| Introduction and<br>High-level<br>Synthesis [Part-<br>1]     | <ul> <li>1) Find the essential prime implicants of the following Boolean function.</li> <li>F = a'bc + ab'c + abc + abc'</li> <li>bc, ab, bc'</li> <li>bc, ab, ac</li> </ul>                                                                                                   | 1 poin  |

| Introduction and<br>High-level<br>Synthesis [Part-<br>2]     | bc', ab, a'c' bc, ab', ac  No, the answer is incorrect.                                                                                                                                                                                                                        |         |

| RTL<br>Optimizations<br>[Part-1]                             | Score: 0  Accepted Answers: bc, ab, ac                                                                                                                                                                                                                                         |         |

| RTL<br>Optimizations<br>[Part-2]                             | 2) Which one of the following cubes is a kernel of the function F = abc + abd + bcd?  abc + abd + bcd  bc + bd                                                                                                                                                                 | 1 poin  |

| Logic Synthesis<br>and Physical<br>Synthesis                 | ac + ad + cd  None of the above.                                                                                                                                                                                                                                               |         |

| <ul><li>Introduction to<br/>Logic Synthesis</li></ul>        | No, the answer is incorrect. Score: 0                                                                                                                                                                                                                                          |         |

| Overview of FPGA Technology Mapping                          | Accepted Answers:  ac + ad + cd  3) Which one of the following statement is NOT correct about Boolean functions?                                                                                                                                                               | 1 poin  |

| <ul><li>Introduction to<br/>Physical<br/>Synthesis</li></ul> | <ul> <li>Boolean function can be implemented with only prime implicants.</li> <li>Essential prime implicant covers a minterm that is not covered by any other prime implicant.</li> <li>An irredundant cover is a cover that is not a proper superset of any cover.</li> </ul> |         |

| <ul><li>Quiz :     Assignment for     Week 4</li></ul>       | Don't care is an input combination that may or may not occur.  No, the answer is incorrect.                                                                                                                                                                                    |         |

| <ul><li>Solution of<br/>Assignment 4</li></ul>               | Score: 0                                                                                                                                                                                                                                                                       |         |

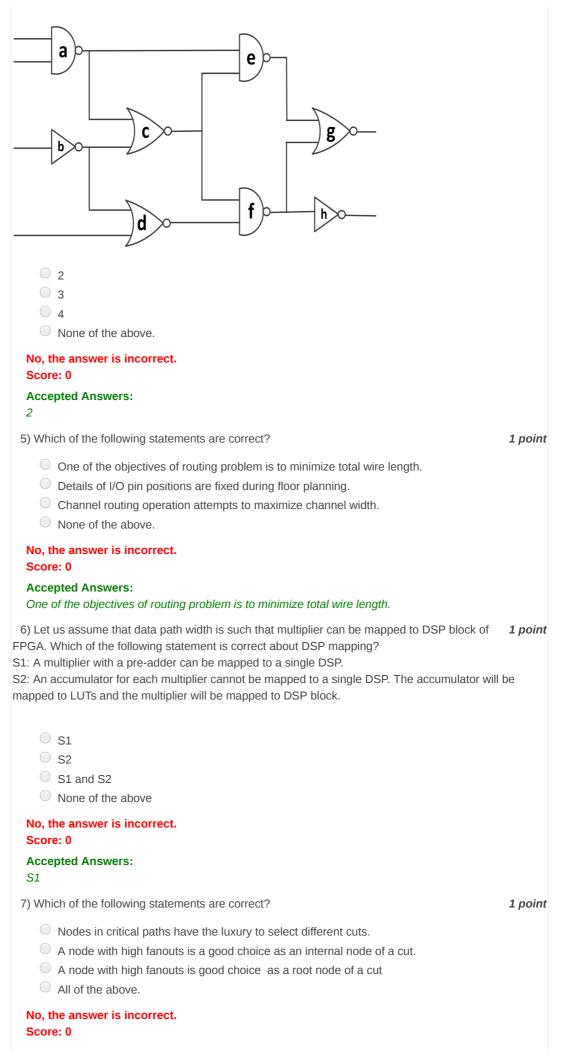

| VLSI Testing [Part-1]                                        | Accepted Answers:  Don't care is an input combination that may or may not occur.  4) Consider the following gate level design. Find the minimum 4 input LUTs required to                                                                                                       | 1 poin  |

| VLSI Testing<br>[Part-2]                                     | implement it in FPGA?                                                                                                                                                                                                                                                          |         |

2]

Verification [Part-1]

Verification [Part-

#### **Accepted Answers:**

A node with high fanouts is good choice as a root node of a cut

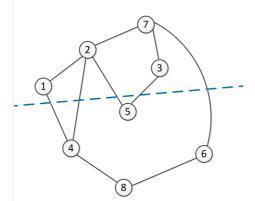

8) Consider the graph with initial partition shown through the cut line. After application of one **1** point iteration of the inner loop of Kernighan-Lin (KL) algorithm on this circuit results in the final cut with size is \_\_\_\_. Assume that each edge weight is one.

- **5**

- 0 4

- 3

- 2

No, the answer is incorrect.

Score: 0

## **Accepted Answers:**

3

9) For the graph in question 8, the partition resulting from KL algorithm is,

1 point

- Partition 1: {1, 4, 6, 8}; Partition 2: {2, 3, 5, 7}

- Partition 1: {1, 2, 3, 8}; Partition 2: {4, 5, 6, 7}

- Partition 1: {1, 2, 3, 4}; Partition 2: {5, 6, 7, 8}

- None of the above.

No, the answer is incorrect.

Score: 0

### **Accepted Answers:**

Partition 1: {1, 4, 6, 8}; Partition 2: {2, 3, 5, 7}

Previous Page

Enc

© 2014 NPTEL - Privacy & Terms - Honor Code - FAQs -

A project of

In association with

Funded by

Government of India Ministry of Human Resource Development

Powered by