## NPTEL

reviewer1@nptel.iitm.ac.in ▼

### Courses » Optimization Techniques for Digital VLSI Design

Announcements Course Ask a Question Progress Mentor

# Unit 1 - How to access the portal

| Course                                                                        | Assignment for Week 0                                                                                                            |    |

|-------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------|----|

| Juline                                                                        | The due date for submitting this assignment has passed. Due on 2018-01-20, 00:00 I                                               | ST |

| How to access<br>the portal                                                   | Submitted assignment                                                                                                             |    |

| Lesson 1: How to access the home page?                                        | How many full adders and half adders are required to construct an m-bit parallel adder?      m/2 full adders and m/2 half adders | ро |

| Lesson 2: How to access the course page?                                      | m half adders m-1 full adders and 1 half adder m+1 half adders                                                                   |    |

| Lesson 3: How<br>to access the<br>MCQ, MSQ and<br>Programming<br>assignments? | No, the answer is incorrect.  Score: 0  Accepted Answers:  m-1 full adders and 1 half adder                                      |    |

| Quiz :<br>Assignment for<br>Week 0                                            |                                                                                                                                  | po |

| ntroduction and<br>High-level<br>Synthesis [Part-<br>L]                       | 3<br>4<br>5                                                                                                                      |    |

| ntroduction and<br>High-level<br>Synthesis [Part-<br>2]                       | No, the answer is incorrect. Score: 0 Accepted Answers:                                                                          |    |

| RTL<br>Optimizations<br>Part-1]                                               | 2 inputs and 2 outputs                                                                                                           | ро |

| RTL<br>Optimizations<br>Part-2]                                               | 1 input and 2 outputs 1 input and 1 output None of the above                                                                     |    |

| Logic Synthesis<br>and Physical<br>Synthesis                                  | No, the answer is incorrect.  Score: 0  Accepted Answers:                                                                        |    |

| /LSI Testing<br>Part-1]                                                       | 1 input and 2 outputs                                                                                                            | рс |

| /LSI Testing<br>Part-2]                                                       | Z/4 MHz                                                                                                                          |    |

Optimization Techniques for Digital VLSI Design - - Unit 1 - How to access the portal

Verification [Part-1]

Verification [Part-2] No, the answer is incorrect.

Score: 0

#### **Accepted Answers:**

X/32 MHz

X/320 MHz

X/320 MHz

5) Which of the following describes most appropriately a "shift register"

1 point

- The register that can shift information bits to another register

- The register that can shift information bits either to the right or to the left

- The register that can shiftin formation bits to the right only

- The register that can shift information bits to the left only

#### No, the answer is incorrect.

Score: 0

#### **Accepted Answers:**

The register that can shift information bits either to the right or to the left

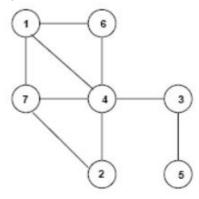

6) What is the chromatic number of the following graph?

1 point

- 0 1

- 2

- 3

- 0 4

No, the answer is incorrect.

Score: 0

## **Accepted Answers:**

3

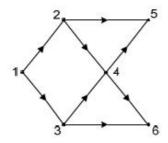

7) Consider the DAG with  $V = \{1, 2, 3, 4, 5, 6\}$  below. Which one the following is NOT a topological ordering?

1 point

- 123456

- 132456

- 132465

- 324165

| No, the answer is incorrect.                                                                                                               | cai             |       |

|--------------------------------------------------------------------------------------------------------------------------------------------|-----------------|-------|

| Score: 0                                                                                                                                   |                 |       |

| Accepted Answers: 3 2 4 1 6 5                                                                                                              |                 |       |

| 8) To achieve linear time complexity of Dijkstra's shortest path algorithm on undirect unweighted graphs, the data structure to be used is | ed and <b>1</b> | point |

| Queue Stack Heap B-Tree                                                                                                                    |                 |       |

| No, the answer is incorrect. Score: 0                                                                                                      |                 |       |

| Accepted Answers: Queue                                                                                                                    |                 |       |

| 9) A Language for which a DFA can be constructed is a                                                                                      | 1               | point |

| Regular Language Context free Language Recursively enumerable language None of the above                                                   |                 |       |

| No, the answer is incorrect. Score: 0                                                                                                      |                 |       |

| Accepted Answers: Regular Language                                                                                                         |                 |       |

| 10)n the formal definition of a deterministic finite state machine the number of tuples                                                    | required is 1   | point |

| <ul><li>4</li><li>5</li><li>6</li><li>7</li></ul>                                                                                          |                 |       |

| No, the answer is incorrect.<br>Score: 0                                                                                                   |                 |       |

| Accepted Answers: 5                                                                                                                        |                 |       |

| You were allowed to submit this assignment only once.                                                                                      |                 |       |

| Previous Page                                                                                                                              | End             |       |

© 2014 NPTEL - Privacy & Terms - Honor Code - FAQs -

A project of

Funded by

Government of India Ministry of Human Resource Development Powered by