© 2014 NPTEL - Privacy & Terms - Honor Code - FAQs -

## Computer Organization and Architecture A Ped...

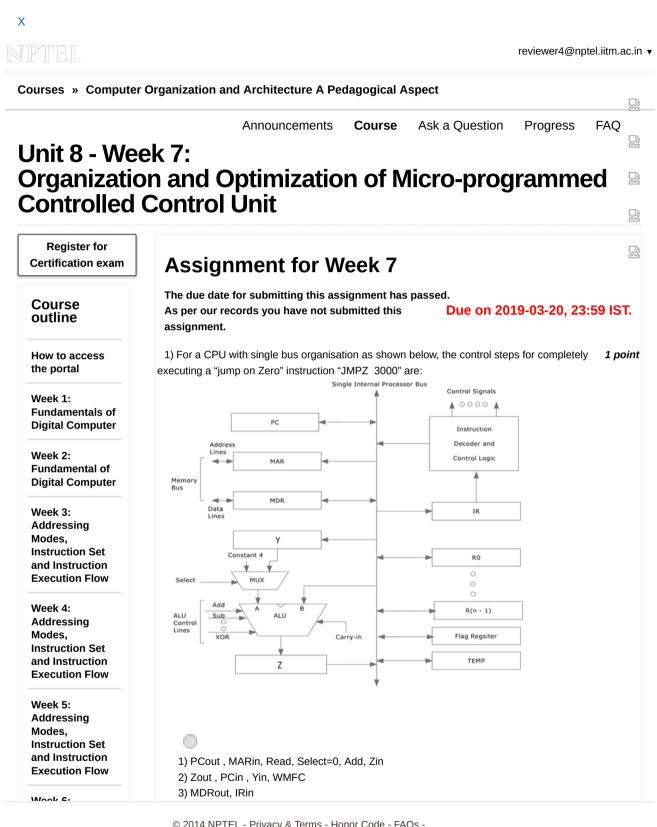

| Organization<br>and Optimization<br>of Micro-<br>programmed<br>Controlled<br>Control Unit            | 5) Zout, PCin<br>1) PCout , MARin, Read, Select=0, Add, Zin<br>2) Zout , PCin , WMFC<br>3) MDRout, IRin                                                                                                                                                                               |             |  |  |  |  |

|------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------|--|--|--|--|

| <ul> <li>Handling<br/>Different<br/>Addressing<br/>Modes</li> </ul>                                  | <ul> <li>4) IRout, R1in</li> <li>1) PCout, MARin, Read, Select=0, Add, Zin</li> <li>2) Zout, PCin, Yin, WMFC</li> </ul>                                                                                                                                                               | 2           |  |  |  |  |

| <ul> <li>Handling</li> <li>Control</li> <li>Transfer</li> <li>Instructions</li> </ul>                | <ul> <li>3) MDRout, IRin</li> <li>4) Offset-field-of-IRout, Select=1, Add, Zin, If Zero Flag!=0 then END</li> <li>5) Zout, PCin</li> </ul>                                                                                                                                            | C<br>c<br>c |  |  |  |  |

| Design of<br>Hardwired<br>controlled<br>Control Unit                                                 | No, the answer is incorrect.<br>Score: 0                                                                                                                                                                                                                                              |             |  |  |  |  |

| Quiz :<br>Assignment for<br>Week 7                                                                   | Accepted Answers:<br>1) PCout , MARin, Read, Select=0, Add, Zin<br>2) Zout , PCin , Yin, WMFC<br>3) MDRout, IRin                                                                                                                                                                      |             |  |  |  |  |

| Week 8:<br>Organization<br>and Optimization<br>of Micro-<br>programmed<br>Controlled<br>Control Unit | <ul> <li>4) Offset-field-of-IRout, Select=1, Add, Zin, If Zero Flag!=0 then END</li> <li>5) Zout, PCin</li> <li>2) For a CPU with single bus organisation shown in question 1, the control steps for completely executing a "jump on negative" instruction "BRN 3000" are:</li> </ul> | 1 poi       |  |  |  |  |

| Week 9: Memory<br>Sub-system<br>Organization                                                         | <ol> <li>PCout , MARin, Read, Select=0, Add, Zin</li> <li>2) Zout , PCin , Yin, WMFC</li> <li>3) MDRout, IRin</li> </ol>                                                                                                                                                              |             |  |  |  |  |

| Week 10:<br>Memory<br>Sub-system<br>Organization                                                     | <ul> <li>4) Offset-field-of-IRout, Select=1, Add, Zin, If Sign Flag!=1 then END</li> <li>1) PCout , MARin, Read, Select=0, Add, Zin</li> <li>2) Zout , PCin , Yin, WMFC</li> </ul>                                                                                                    |             |  |  |  |  |

| Week 11:<br>Memory<br>Sub-system<br>Organization                                                     | <ul> <li>3) MDRout, IRin</li> <li>4) Offset-field-of-IRout, Select=1, Add, Zin, If Sign Flag!=0 then END</li> <li>5) Zout, PCin</li> </ul>                                                                                                                                            |             |  |  |  |  |

| Week 12:<br>Input/output<br>Subsystem                                                                | <ol> <li>PCout, MARin, Read, Select=0, Add, Zin</li> <li>Zout, PCin, Yin, WMFC</li> <li>MDRout, IRin</li> <li>Offset field of IPout, Select=1, Add, Zin, If Cign Flegt=1 then FND</li> </ol>                                                                                          |             |  |  |  |  |

| TEXT<br>TRANSCRIPTS                                                                                  | <ul> <li>4) Offset-field-of-IRout, Select=1, Add, Zin, If Sign Flag!=1 then END</li> <li>5) Zout, PCin</li> <li>None of the above</li> </ul>                                                                                                                                          |             |  |  |  |  |

|                                                                                                      | No, the answer is incorrect.<br>Score: 0<br>Accepted Answers:                                                                                                                                                                                                                         |             |  |  |  |  |

|                                                                                                      | <ul> <li>Accepted Answers:</li> <li>1) PCout , MARin, Read, Select=0, Add, Zin</li> <li>2) Zout , PCin , Yin, WMFC</li> <li>3) MDRout, IRin</li> <li>4) Offset-field-of-IRout, Select=1, Add, Zin, If Sign Flag!=1 then END</li> <li>5) Zout, PCin</li> </ul>                         |             |  |  |  |  |

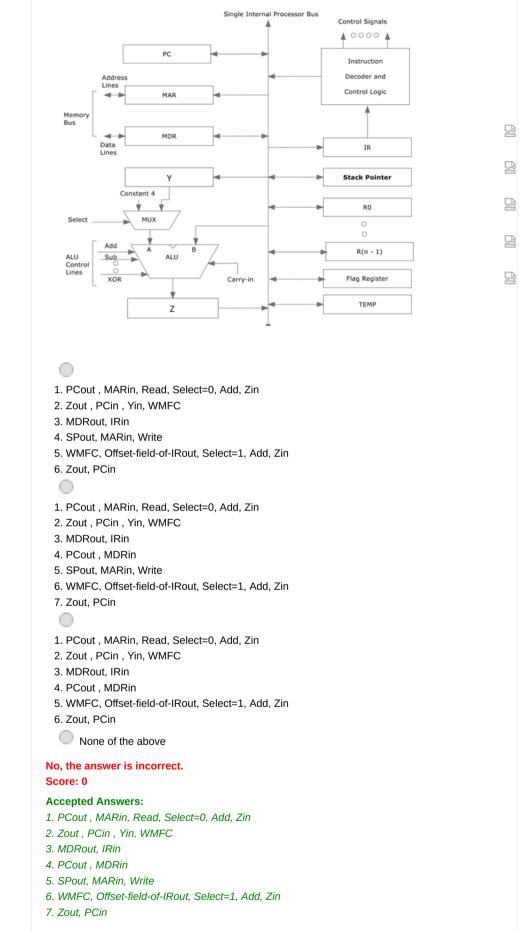

|                                                                                                      | 3) For a CPU with single bus organisation shown below, the control steps for completely executing a "CALL FUNC" instruction are:                                                                                                                                                      | 1 poir      |  |  |  |  |

4) For a CPU with single bus organisation shown in question 3, the control steps for

completely executing a "RETURN" (from function FUNC from question 3) instruction are:

| •                                          |       |  |  |  |  |

|--------------------------------------------|-------|--|--|--|--|

| 1. PCout , MARin, Read, Select=0, Add, Zin |       |  |  |  |  |

| 2. Zout , PCin , Yin, WMFC                 |       |  |  |  |  |

| 3. MDRout, IRin                            |       |  |  |  |  |

| 4. PCout, MARin, Read                      |       |  |  |  |  |

| 5. WMFC                                    |       |  |  |  |  |

| 6. MBRout, PCin                            |       |  |  |  |  |

|                                            | _     |  |  |  |  |

| 1. PCout , MARin, Read, Select=0, Add, Zin |       |  |  |  |  |

| 2. Zout , PCin , Yin, WMFC                 |       |  |  |  |  |

| 3. MDRout, IRin                            |       |  |  |  |  |

| 4. IRout, MARin, Read                      |       |  |  |  |  |

| 5. WMFC                                    | 5     |  |  |  |  |

| 6. MBRout, PCin                            | [Vood |  |  |  |  |

|                                            |       |  |  |  |  |

| 1. PCout , MARin, Read, Select=0, Add, Zin | 200   |  |  |  |  |

| 2. Zout , PCin , Yin, WMFC                 |       |  |  |  |  |

| 3. MDRout, IRin                            |       |  |  |  |  |

| 4. SPout, MARin, Read                      |       |  |  |  |  |

| 5. WMFC                                    |       |  |  |  |  |

| 6. MBRout, PCin                            |       |  |  |  |  |

| None of the above                          |       |  |  |  |  |

| No, the answer is incorrect.               |       |  |  |  |  |

| Score: 0                                   |       |  |  |  |  |

| Accepted Answers:                          |       |  |  |  |  |

| 1. PCout , MARin, Read, Select=0, Add, Zin |       |  |  |  |  |

| 2. Zout , PCin , Yin, WMFC                 |       |  |  |  |  |

| 3. MDRout, IRin                            |       |  |  |  |  |

| 4. SPout, MARin, Read                      |       |  |  |  |  |

| 5. WMFC                                    |       |  |  |  |  |

| 6. MBRout, PCin                            |       |  |  |  |  |

5) Consider the instruction "LOAD R1, M" (Data from memory location M is loaded to register **1** *point* R1). We assume that length of instruction is 1 (constant). The first two control steps used to fetch the instruction "LOAD R1, M" (question 1) are given below

1. PCout , MARin, Read, Select=0, Add, Zin

2. Zout , PCin , WMFC

| After step-1 |       | After step-2 |       |

|--------------|-------|--------------|-------|

| Register     | Value | Register     | Value |

| PC           | Х     | PC           |       |

| MAR          | Х     | MAR          |       |

| MDR          | -     | MDR          |       |

The values in the PC, MAR and MDR after Step 1 is shown above. What are the values of PC, MAR and MDR after Step 2?

PC = X; MAR = X+1; MDR = LOAD R1, M;

PC = X+1; MAR = X; MDR = LOAD R1, M;

PC = X; MAR = X; MDR = LOAD R1, M;

None of the above

No, the answer is incorrect. Score: 0

|          | C = X+1; MAR = X ; MDR = LOAD R1, M;                                                                                                                                                   |     |

|----------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|

|          | Which of the following options represents the action of the 1st control step in question 5 in best manner?                                                                             | 1 p |

|          | Program counter value is assigned to the memory buffer register                                                                                                                        |     |

|          | The memory buffer register waits for memory read operation to be completed                                                                                                             |     |

|          | The memory address register waits for memory read operation to be completed                                                                                                            |     |

|          | None of the above                                                                                                                                                                      |     |

|          | lo, the answer is incorrect.<br>core: 0                                                                                                                                                |     |

| Α        | ccepted Answers:                                                                                                                                                                       |     |

| N        | lone of the above                                                                                                                                                                      |     |

|          | Three control steps (after fetch) are required to execute the instruction "LOAD R1, M" estion 1). Which of the following options describe that sequence of control steps?              | 1 p |

|          | •                                                                                                                                                                                      |     |

|          | 1. IRout, MARin, Read                                                                                                                                                                  |     |

|          | 2. WMFC<br>3. MDRout, R1in                                                                                                                                                             |     |

|          |                                                                                                                                                                                        |     |

|          | 1. WMFC                                                                                                                                                                                |     |

|          | 2. IRout, MARin, Read                                                                                                                                                                  |     |

|          | 3. MDRout, R1in                                                                                                                                                                        |     |

|          | 0                                                                                                                                                                                      |     |

|          | 1. WMFC                                                                                                                                                                                |     |

|          | 2 MDRout, R1in                                                                                                                                                                         |     |

|          | 3. IRout, MARin, Read                                                                                                                                                                  |     |

|          | 0                                                                                                                                                                                      |     |

|          | 1. IRout, MARin, Read                                                                                                                                                                  |     |

|          | 2. WMFC                                                                                                                                                                                |     |

|          | 3. MDRin, R1out                                                                                                                                                                        |     |

|          | lo, the answer is incorrect.<br>core: 0                                                                                                                                                |     |

| Α        | ccepted Answers:                                                                                                                                                                       |     |

|          | . IRout, MARin, Read                                                                                                                                                                   |     |

|          | WMFC                                                                                                                                                                                   |     |

| 3.       | . MDRout, R1in                                                                                                                                                                         |     |

|          | Consider the indirect addressing mode instruction "Load R1, (M)".                                                                                                                      | 1 p |

|          | of the instruction: Load the content of Memory Location M1 to Register R1. There are five<br>(after fetch) that are required to execute the instruction "LOAD R1, (M)", as shown below |     |

| siep     |                                                                                                                                                                                        | v.  |

| 1.       |                                                                                                                                                                                        |     |

| 2.       | WMFC                                                                                                                                                                                   |     |

| 3.       | MDRout, MARin                                                                                                                                                                          |     |

| 4.<br>5. | WMFC<br>MDRout P1in                                                                                                                                                                    |     |

| J.       | MDRout, R1in                                                                                                                                                                           |     |

| Whi      | ch of the following describes most appropriately, the step marked above with?                                                                                                          |     |

|          |                                                                                                                                                                                        |     |

Computer Organization and Architecture A Ped...

| <ul><li>Zout , PCin</li><li>IRout, MARin, Read</li></ul>                            |         |

|-------------------------------------------------------------------------------------|---------|

| No, the answer is incorrect.<br>Score: 0<br>Accepted Answers:<br>IRout, MARin, Read |         |

|                                                                                     | <u></u> |

| Previous Page                                                                       | End 🗟   |

|                                                                                     | 뮲       |

|                                                                                     | 뮲       |