reviewer4@nptel.iitm.ac.in ▼ Courses » Computer Organization and Architecture A Pedagogical Aspect **Announcements** Course Ask a Question **Progress** FAQ **Unit 7 - Week 6: Organization and Optimization of Micro-programmed Controlled Control Unit** Register for **Assignment for Week 6 Certification exam** The due date for submitting this assignment has passed. Course As per our records you have not submitted this Due on 2019-03-13, 23:59 IST. outline assignment. 1) The clock-cycle grouping in the fetch cycle could How to access 1 point the portal Avoid conflicts between operations Week 1: Maintain the proper sequencing of instructions **Fundamentals of Digital Computer** Save time for the fetch cycle All of the above Week 2: Fundamental of No, the answer is incorrect. Digital Computer Score: 0 **Accepted Answers:** Week 3: Addressing All of the above Modes. 2) Which of the following is NOT a micro-operation? Instruction Set 1 point and Instruction **Execution Flow** Register transfer Arithmetic Week 4: Addressing Loop Modes, **Instruction Set** Shift and Instruction No. the answer is incorrect. **Execution Flow** Score: 0 Week 5: **Accepted Answers:** Addressing Modes, Instruction Set 1 point 3) The fetch cycle consists of 4 micro-operations given below and Instruction **Execution Flow** t2: MEMORY → MBR Maak 6. © 2014 NPTEL - Privacy & Terms - Honor Code - FAQs -In association with A project of

Funded by

## No, the answer is incorrect.

## Score: 0

## **Accepted Answers:**

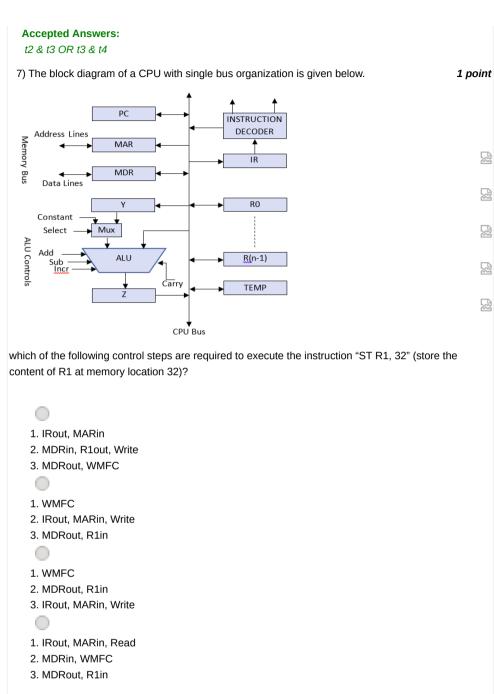

- 1. IRout, MARin

- 2. MDRin, R1out, Write

- 3. MDRout, WMFC

- 8) The first three steps used to fetch the instruction "ADD R1, R2" (In the CPU with single bus **1** point organization shown in question 7) are given below

- 1. PCout, MARin, Read, Select=0, Add, Zin

- 2. Zout , PCin , WMFC

- 3. MDRout, IRin

| After step                                                                                                        | -1                                                                     | After step-2                                                          |                        |     | After step-3 |            |                     |

|-------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------|-----------------------------------------------------------------------|------------------------|-----|--------------|------------|---------------------|

| Register                                                                                                          |                                                                        |                                                                       | Value                  |     | Register     | Value      |                     |

| PC                                                                                                                | Х                                                                      | PC                                                                    | X+1                    |     | PC           |            |                     |

| MAR                                                                                                               | Х                                                                      | MAR                                                                   | Χ                      |     | MAR          |            |                     |

| MDR                                                                                                               | -                                                                      | MDR                                                                   | ADD<br>R2.             | R1, | MDR          | ADD<br>R2. | R1,                 |

| IR                                                                                                                | -                                                                      | IR                                                                    | -                      |     | IR           |            |                     |

| PC = >                                                                                                            | AR and IR a X+1; MAR = X+1; MAR = X; MAR =X of the above yer is incorr | after Step 3?<br>= X ; IR= ADD F<br>=X+1 ; IR = ADI<br>; IR = ADD R1, | R1, R2.;<br>D R1, R2.; |     |              |            |                     |

| 9) What is the (in the CPU with 1.PCout, MARir 2. Zout, PCin, V 3. MDRout, IRin 4. R2out, Yin 5. R1out, Select 6. | single bus<br>n, Read, Sel<br>WMFC                                     | lect=0, Add, Zir                                                      | own in que             |     | -            | n ""ADD R  | 1, R2"" <b>1 pc</b> |

| Zin, R                                                                                                            | 1in                                                                    |                                                                       |                        |     |              |            |                     |

|                                                                                                                   | ut, R1in                                                               |                                                                       |                        |     |              |            |                     |

| Yin, Ri                                                                                                           |                                                                        |                                                                       |                        |     |              |            |                     |

| No, the answ<br>Score: 0                                                                                          |                                                                        | rect.                                                                 |                        |     |              |            |                     |

| Accepted An<br>Zout, R1in                                                                                         | swers:                                                                 |                                                                       |                        |     |              |            |                     |

| Previ                                                                                                             | ious Pa                                                                | ge                                                                    |                        |     |              |            | End                 |