© 2014 NPTEL - Privacy & Terms - Honor Code - FAQs -

## Computer Organization and Architecture A Ped...

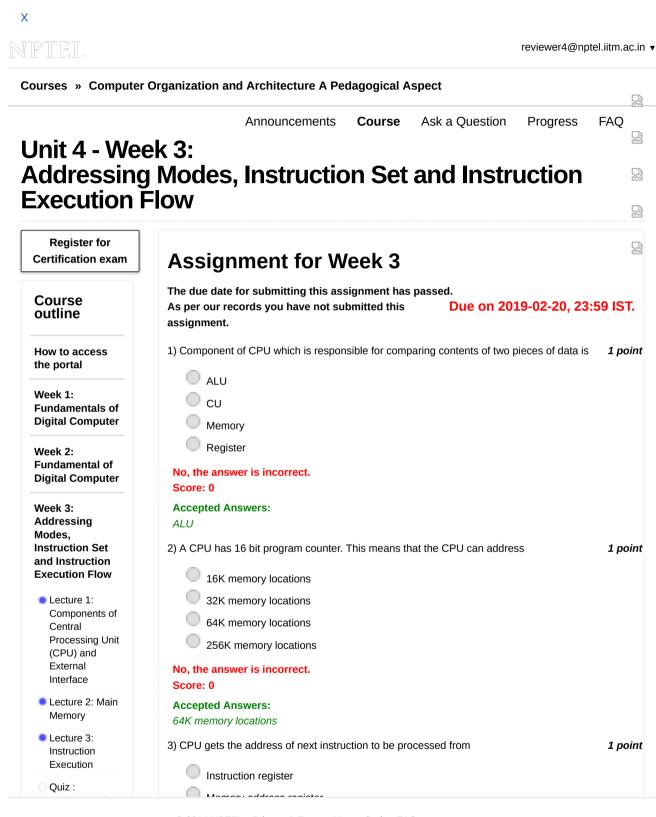

| Week 5:                            | 4) On getting an interrupt, CPU 0                                                                            | points      |

|------------------------------------|--------------------------------------------------------------------------------------------------------------|-------------|

| Addressing                         |                                                                                                              |             |

| Modes,                             | finishes the current instruction and moves to interrupt service routine                                      |             |

| Instruction Set<br>and Instruction | immediately moves to interrupt service routine without completing current instruction                        |             |

| Execution Flow                     | releases the control on I/O lines and memory lines                                                           |             |

| Week 6:<br>Organization            | makes the peripheral device, which requested the interrupt wait for fixed interval of time                   | e 🖉         |

| and Optimization                   | No, the answer is incorrect.<br>Score: 0                                                                     | 2           |

| of Micro-                          |                                                                                                              | 2           |

| programmed<br>Controlled           | Accepted Answers:<br>immediately moves to interrupt service routine without completing current instruction   | 2           |

| Control Unit                       |                                                                                                              | ⊔<br>1 poin |

| Week 7:                            | 5) The module which is not part of CPO.                                                                      |             |

| Organization                       | Arithmetic processing unit                                                                                   |             |

| and Optimization<br>of Micro-      | General purpose registers                                                                                    | ~           |

| programmed                         | Main memory                                                                                                  |             |

| Controlled<br>Control Unit         | Control unit                                                                                                 |             |

|                                    | No, the answer is incorrect.                                                                                 |             |

| Week 8:<br>Organization            | Score: 0                                                                                                     |             |

| and Optimization                   | Accepted Answers:                                                                                            |             |

| of Micro-<br>programmed            | Main memory                                                                                                  |             |

| Controlled                         |                                                                                                              |             |

| Control Unit                       | 6) Suppose the size of the Main Memory is 16K * 8 bits. What are the sizes of address bus and data bus?      | 1 poin      |

| Week 9: Memory                     |                                                                                                              |             |

| Sub-system                         | Address bus = 16 bits, Data bus = 8 bits                                                                     |             |

| Organization                       | Address bus = 14 bits, Data bus = 3 bits                                                                     |             |

| Week 10:                           | Address bus = 16 bits, Data bus = 3 bits                                                                     |             |

| Memory<br>Sub-system               | Address bus = 14 bits, Data bus = 8 bits                                                                     |             |

| Organization                       | No, the answer is incorrect.                                                                                 |             |

| Week 11:                           | Score: 0                                                                                                     |             |

| Memory<br>Sub-system               | Accepted Answers:                                                                                            |             |

| Organization                       | Address bus = 14 bits, Data bus = 8 bits                                                                     |             |

| Week 12:                           | 7) How many memory chips of configuration 1K x 8 Bits are required to implement an 8K x 32 2<br>Bits memory? | 1 poin      |

| Input/output<br>Subsystem          | <b>4</b>                                                                                                     |             |

|                                    | 08                                                                                                           |             |

| TEXT<br>TRANSCRIPTS                |                                                                                                              |             |

|                                    |                                                                                                              |             |

|                                    | 32                                                                                                           |             |

|                                    | No, the answer is incorrect.<br>Score: 0                                                                     |             |

|                                    | Accepted Answers:                                                                                            |             |

|                                    | 32                                                                                                           |             |

|                                    |                                                                                                              | 1 poin      |

|                                    | O 32                                                                                                         |             |

|                                    |                                                                                                              |             |

|                                    |                                                                                                              |             |

| 256                                                                   |         |

|-----------------------------------------------------------------------|---------|

| No, the answer is incorrect.<br>Score: 0                              |         |

| Accepted Answers:<br>64                                               |         |

| 9) The return address from the interrupt-service routine is stored on | 1 point |

| System heap                                                           | 22      |

| Processor register                                                    |         |

| Processor stack                                                       | _       |

| None of the Above                                                     |         |

| No, the answer is incorrect.<br>Score: 0                              |         |

| Accepted Answers:<br>Processor stack                                  |         |

| 10When a user starts a program, it is:                                | 1 point |

| Ioaded into the CPU                                                   |         |

| erased from the hard drive.                                           |         |

| loaded into RAM.                                                      |         |

| temporarily removed from the registers                                |         |

| No, the answer is incorrect.<br>Score: 0                              |         |

| Accepted Answers:<br>loaded into RAM.                                 |         |

|                                                                       |         |

Previous Page

End