L-23 Slide .

Slide: 01

Quiz Cum Test. II

30th October 2014

Time: 8.45 pm to 10.00 PM

Venue: 010001 and 010002

Course: "After Mid. sem till 29th October

"No" SHEET · during Exam

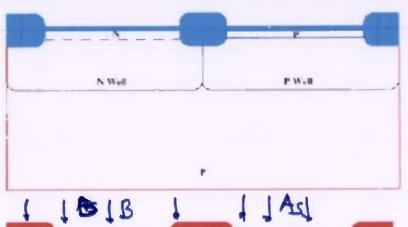

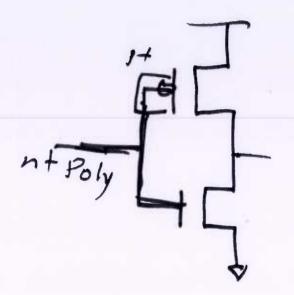

### **Polysilicon Gate Realization**

PWell

CDEEP IIT Bombay

EE 669 L<sup>22</sup> / Slide | 6

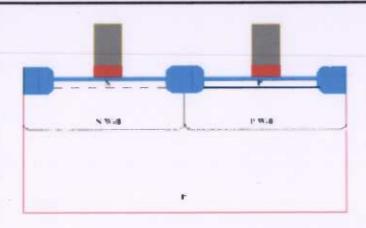

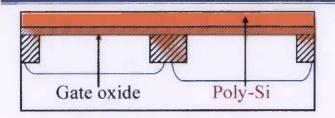

Gate Stack Formation

N Mall

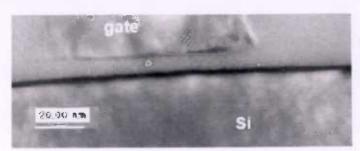

Etch back thin oxide and grow clean gate oxide ~ 5 nm, which can be grown at 800°C in ~ 1 hr.

Nitrided oxides are typical today, and alternative high-K dielectrics are also being considered for Sub 90 nm, Node

LPCVD polysilicon gate deposition (~0.1 microns).

Either masked or unmasked polysilicon doping implant is then performed (target dose such that final average poly doping is > 10<sup>20</sup> cm<sup>-3</sup>).

Rs 10-20 ohm/0

Dry Oxidation

Doping of

Poly.

Ilm Situ duriup

Poly deposition

2 Solid State Diff.

3. Implant

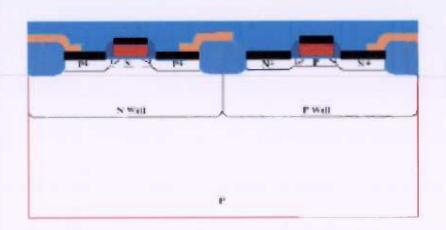

#### **Gate Delineation**

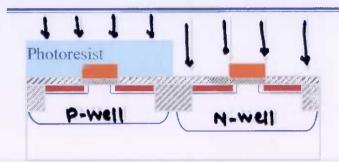

Gate etch: Mask #6 is used to protect the MOS gates. The polysilicon is plasma etched using an anisotropic etch which stops on the underlying oxide.

Process option: gate re-oxidation (to improve reliability in very thin gate oxide devices). Must be done carefully to avoid formation of non-uniform gate oxide thickness:

K. Rim, Ph.D. thesis, Stanford Univ.

EE 669 L 22 / Slide 17

EE 669 L\_\_\_\_ / Slide\_\_\_\_

PIG

Y Tark

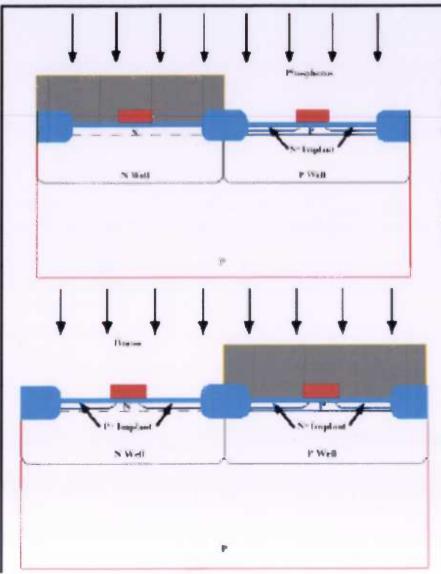

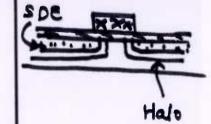

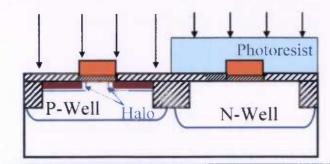

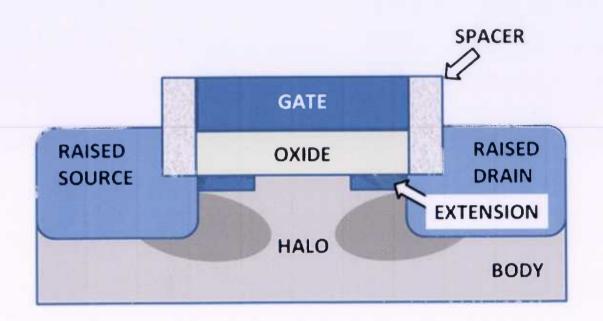

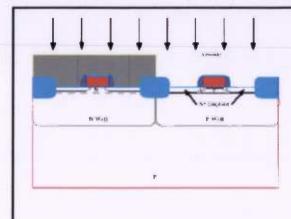

### S/D Extensions for SCE reduction

NMOS S/D Extension formation:

Original concept was Lightly Doped

Drain (LDD) to help deal with hot EE

electron effects. Today, the S/D

extension serves to mitigate

short channel effects. Mask #7

protects the PMOS devices. An As+

implant forms the LDD regions in

the NMOS devices.

PMOS S/D Extension formation:

Mask #8 protects the PMOS devices.

A B+ implant forms the LDD or extension regions.

CDEEP IIT Bombay

EE 669 L<u>22</u> / Slide <u>\</u>

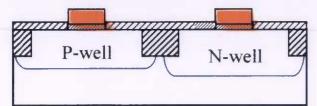

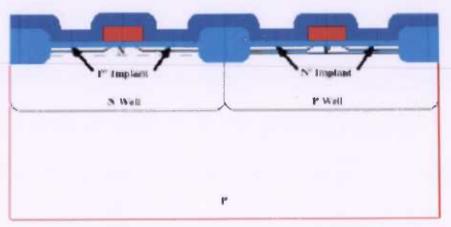

#### **CMOS** Fabrication

- 4 Gate formation:

- Clean silicon surface

- grow gate oxide

- deposit poly-Si gate electrode.

- 5 Mask #4: Gate definition

- etch poly-Si

- etch oxide

- grow masking oxide.

- 6 Mask #5: N+ source / drain extension (SDE) and p-halo:

- As SDE implant

- B/BF2 halo implant

- clean.

Halo

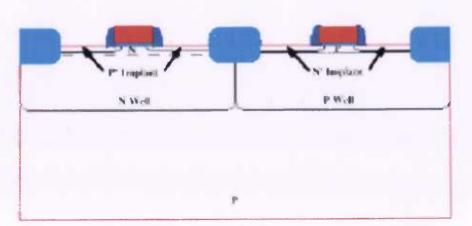

#### CMOS Fabrication

EE 669 L 23 / Slide 7

- B Deep s/d (DSD) formation

- spacer deposition and etch

- Mask #7 N+ DSD

- As implant

- Mask #8 P+ DSD

- B/BF2 implant

- dopant activation (RTA)

- 9 Interconnection

- Mask #9- contact opening

- Mask #10: define metal

S Saba

Santa Clara University

HO #14: ELEN 251 - MOSFET Fundamental

Proper t

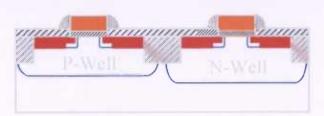

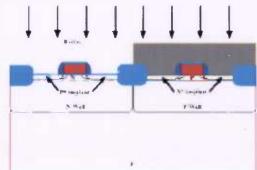

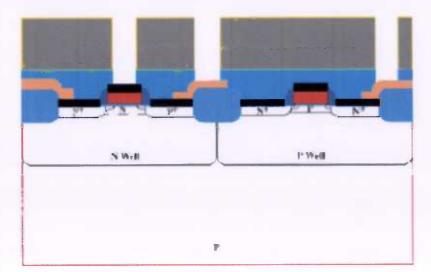

### Sidewall Spacer creation

• Sidewall spacer formation (oxide):

A conformal layer of  $SiO_2$  is EE 669 Ldeposited (typically ~ 0.1 to 0.25 microns thick) LPCVD Process.  $R_{nt} \quad R_n \quad R_n$

CDEEP IIIT Bombay

#### · Sidewall formation:

Anisotropic etching leaves behind "sidewall spacers" along the sides of the polysilicon gates.

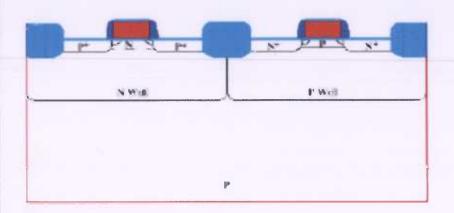

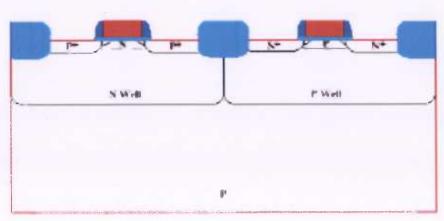

### **Deep Source & Drain Formation**

EE 669 L 23 / Slide 10

• NMOS Deep Source/Drain formation: Mask #9 protects the PMOS devices. An As+ implant forms the NMOS source and drain regions ("deep" = where the silicide contacts will form). Typical conditions are 2 - 4 x 10<sup>15</sup> cm<sup>-2</sup> @ 75 KeV

• PMOS Deep Source/Drain formation: Mask #10 protects the NMOS devices. A B+ implant forms the PMOS source and drain regions. Typical conditions are 1 - 3 x 10<sup>15</sup> cm<sup>-2</sup> @ 50 KeV.

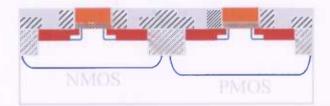

### Source & Drain Contact windows

CDEEP IIT Bombay

• Final anneal: High temperature 669 L 23 / Slide ( drive-in activates the implanted dopants and diffuses junctions to their final depths. Typical conditions: 30 min. @ 900C or 1 min RTA at 1000C.

· Contact formation: Unmasked oxide etch (HF dip) opens regions where contacts will be made to the Si and polysilicon.

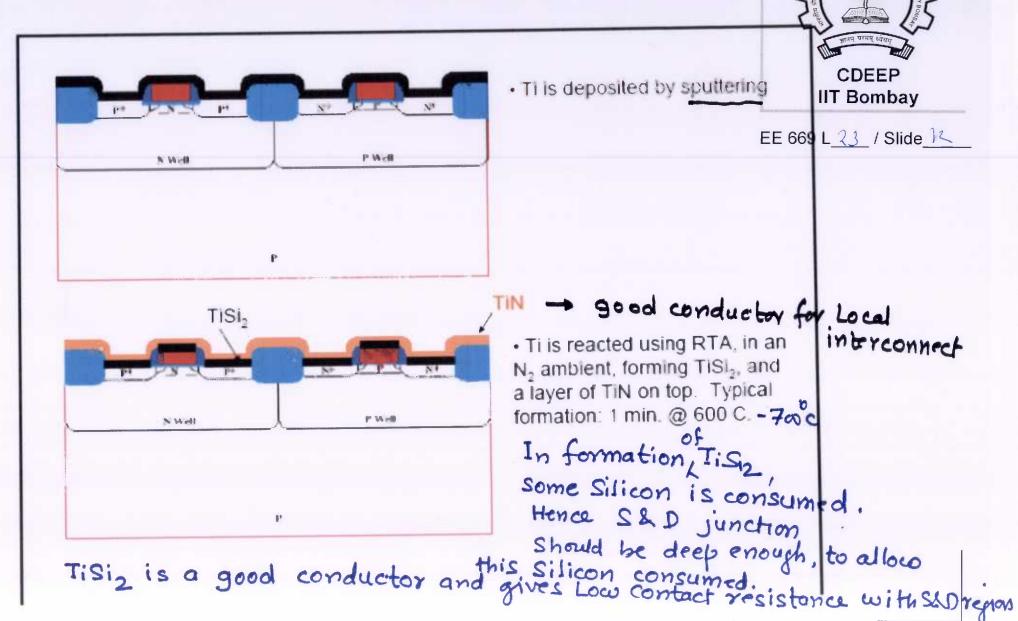

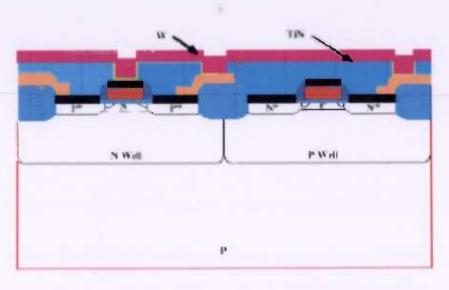

## Titanium Silicide contact to Source and Drain And Titanium Nitride Barrier creation

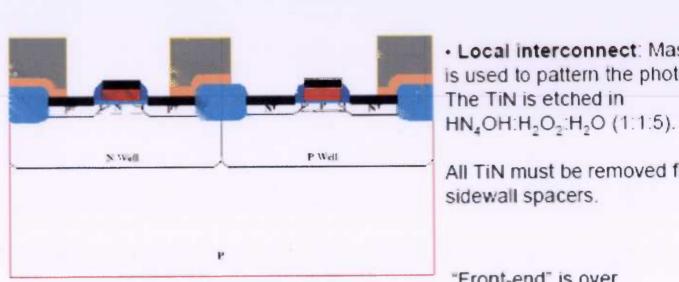

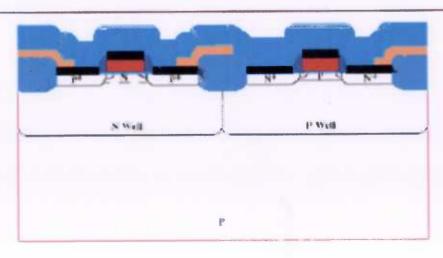

## Local Interconnect to Multilevel Metal

CDEEP.

IIT Bombay Local interconnect: Mask #11 is used to pattern the photoresists L 23 / Slide 13 The TiN is etched in

All TiN must be removed from the sidewall spacers.

"Front-end" is over

Ph - Na B- Glass Floco

· Multilevel metal formation:

A conformal layer of oxide is deposited by LPCVD (~ 1 micron). This is sometimes a phosphosilicate glass, rather than more silicon dioxide.

Sometimes glass could be Borophosphosilicate Glass as well.

BACK-END Processing Starts

# CMP Planerization of Deposited Oxide and Via creation for W-stub

• Chemical mechanical polishing (CMP) is used to planarize the EE 669 L3 / Slide 14 wafer surface.

High Ph-value Silica Slumy is used for CMP.

CDEEP IT Bombay

#### ·Contact hole definition:

Mask #12 is used to define the contact holes. The oxide is etched down to the TiN layers to be contacted.

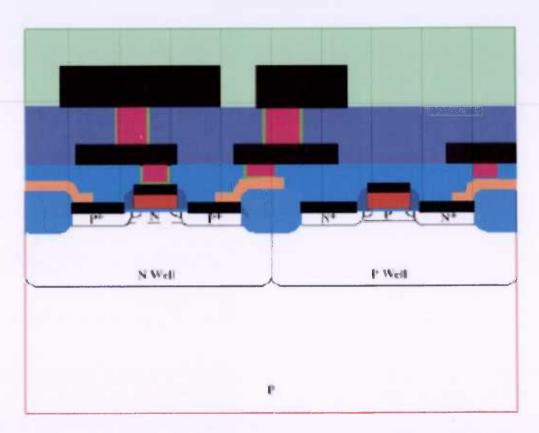

### Deposition of TiN Barrier and Tungsten for Stub Creation

P Wall

Note of

by sputtering (~ few hundred Angstrom), followed by tungsten (W) CVD deposition.

CMP is used to planarize the wafer surface, completing the damascene process.

First Level Global Interconnect Metallization

#### · First level metal:

Al is deposited on the wafer by sputtering. Resist is applied and mask #13 is used to define the first level of metal patterns. The Al is then plasma etched.

EE 669 L 23 / Slide 16

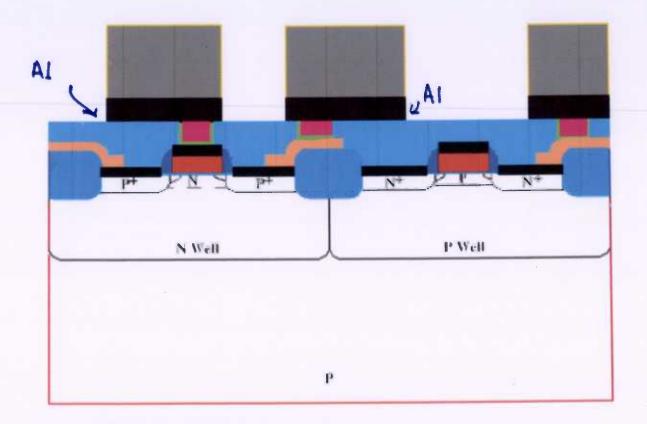

#### **Final Structure**

Second level metal: deposited and defined in the same way as Al level 1.

Mask #14 is used to define contact vias and Mask #15 is used to define metal level 2. A final passivation layer of nitride is deposited by PECVD and patterned with Mask #16.

EE 669 L 23 / Slide 17