Recessed Trenched Oxide Isolation (STI)

L22 / Slide 1-2

#### A Semiconductor

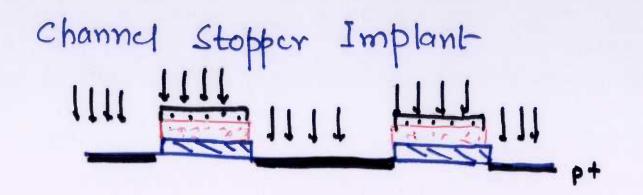

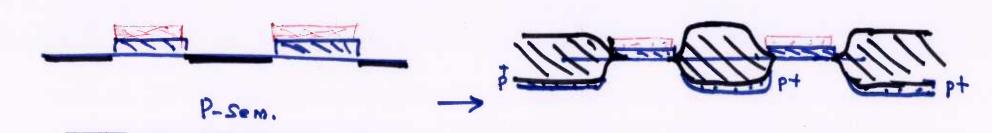

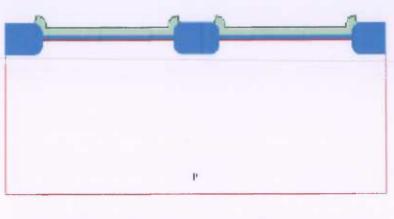

LOCOS PROCESS after Implant 4 removal of Resist.

$$V_{TF} = 2\phi_{12} + \phi_{ms} - \frac{Q_{ox}}{C_{ox}} - \frac{Q_{B}}{C_{ox}}$$

$$Q_{B} = Q_{B} + Q_{implant}$$

$$Q_{Cox} = Q_{implant}$$

$$Q_{$$

: 20HH

EE 669 L 22 / Slide 82

# CMOS Process steps

#### Acknowledgements

Most of the PPTs used here are taken from Work of Prof. Jim Plummer of Stanford University.

EE 669 L 22 / Slide 4

## His book on "Silicon VLSI Technology" is being used as one of the Text Books for the Course of EE 669:VLSI TECHNOLOGY

Similar slides are also available from the course PPTs of VLSI Technology, a Graduate Course offered by Ms. Hoyt At

Massachusetts Institute of Technology, Cambridge, USA -----A.N.Chandorkar, IIT Bombay, Mumbai, INDIA July to November 2014

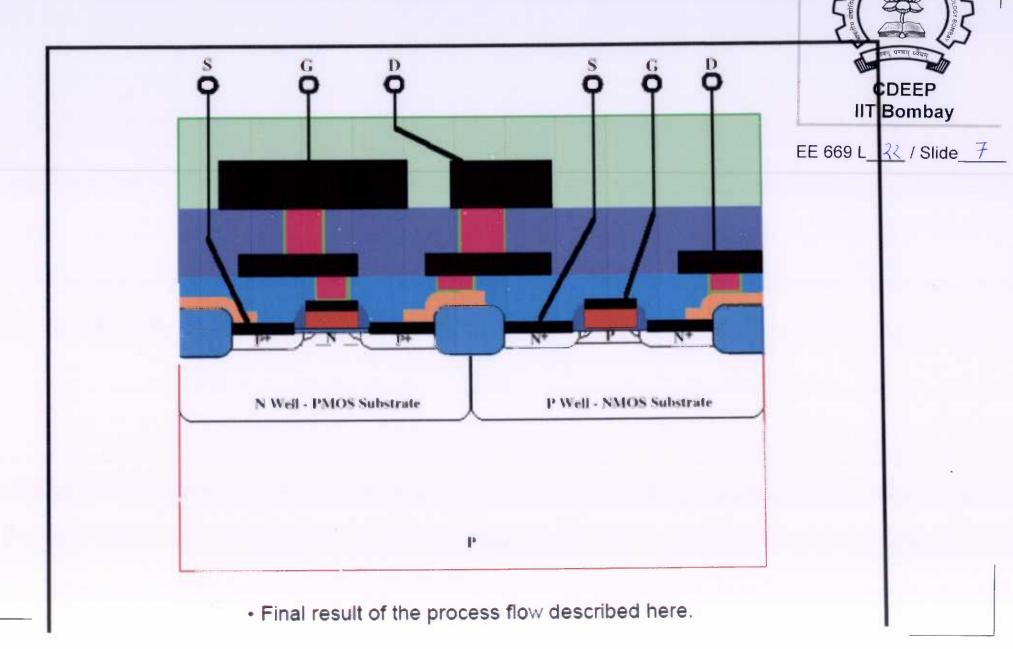

## Standard 16-Mask CMOS Process

CDEEP

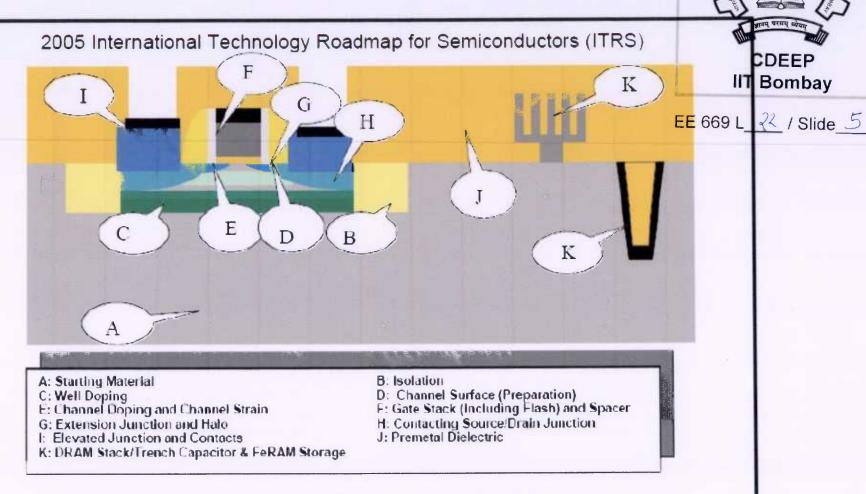

Figure 55 Front End Process Chapter Scope

From "Front-end Processes" (FEP) Chapter, Downloaded 9/5/2006 from http://www.itrs.net/Links/2005ITRS/FEP2005.pdf

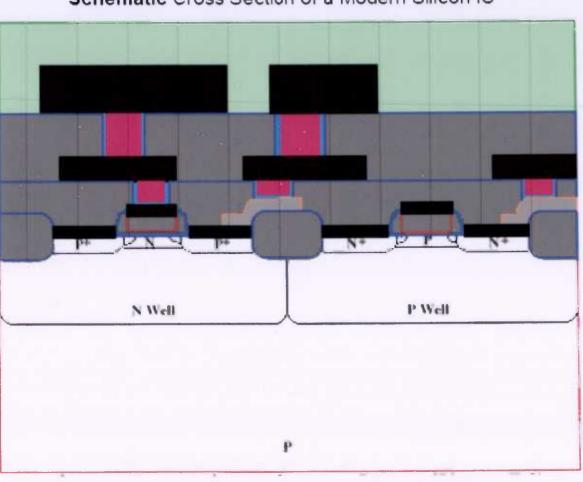

## Overall Structure of CMOS

Schematic Cross Section of a Modern Silicon IC

"Metal 2"

"Metal 1"

(only two levels of wiring shown, for simplicity)

EE 619 L 22 / Slide 6

## Two Level Metal Interconnect CMOS

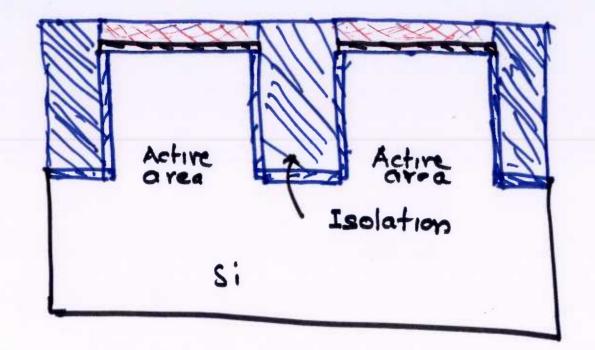

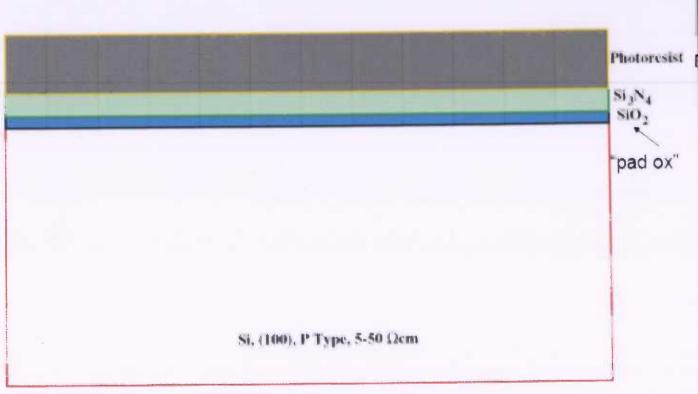

Step-I: "Active Area" Processes

Substrate: moderately high resistivity, (100) Si, p-type

• Active region formation: wafer cleaning, thermal oxidation (~40 nm), silicon nitride deposition (LPCVD) ~ 80 nm, photoresist coat (~0.5 - 1 micron)

• LPC $\lor$ D Si $_3$ N $_4$  is under tensile stress; compressive stress of thermal SiO $_2$  helps to balance this to reduce the stresses in the substrate (defect formation)

CDEEP IIT Bombay

EE 669 L\_22 / Slide 8

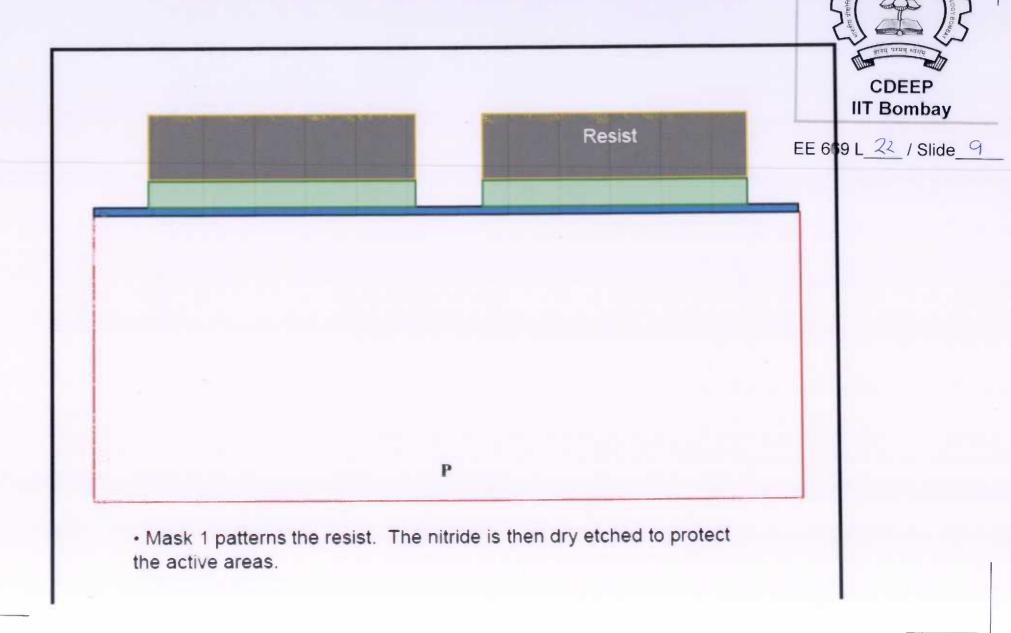

## **Active Area Delineation**

EE 669 L\_2-22/ Slide 10

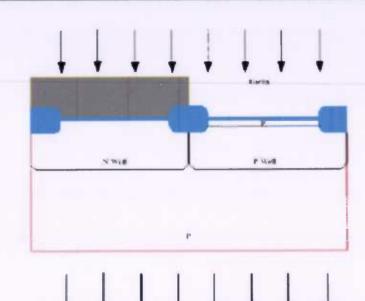

#### **LOCOS** and P-well creation

CDEEP IIT Bombay

• LOCOS: after resist stripping 669 L

L / Slide // Slide /

Strip Nitride layer.

· P Well Formation:

Mask #2 blocks a B+ ion implant to form the wells for the NMOS devices. Typical conditions are 10<sup>13</sup> cm<sup>-2</sup> @ 150 to 200 KeV (to yield final well concentration of ~ 10<sup>17</sup> cm<sup>-3</sup>).

PPR - Clear field Mask

P-Well Mask

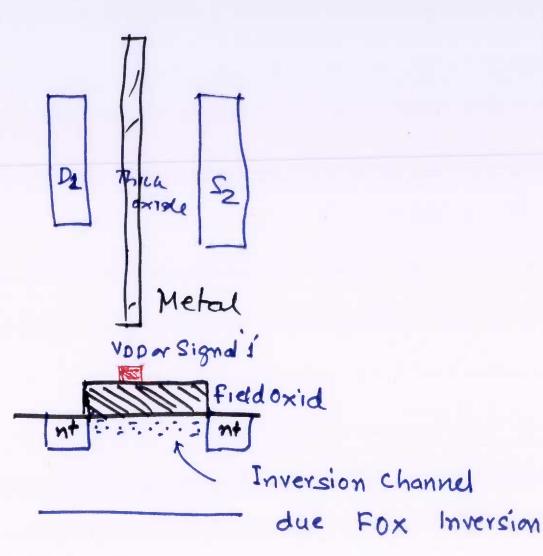

### **Shallow Trench Isolation (STI)**

#### Outline of Shallow Trench Isolation (STI) Process (in place of LOCOS)

· minimal encroachment allows tighter packing of devices

(1) After resist patterning, etch nitride, oxide, and ~ 0.5 micron deep Si trench

(2) Growth of thermal oxide 'liner' in the trenches. Nitride protects top of wafer surface.

(3) CVD of thick SiO2 layer (requires good gap fill)

(4) After CMP planarization

IIT Bombay

EE 669 L < / / Slide / <

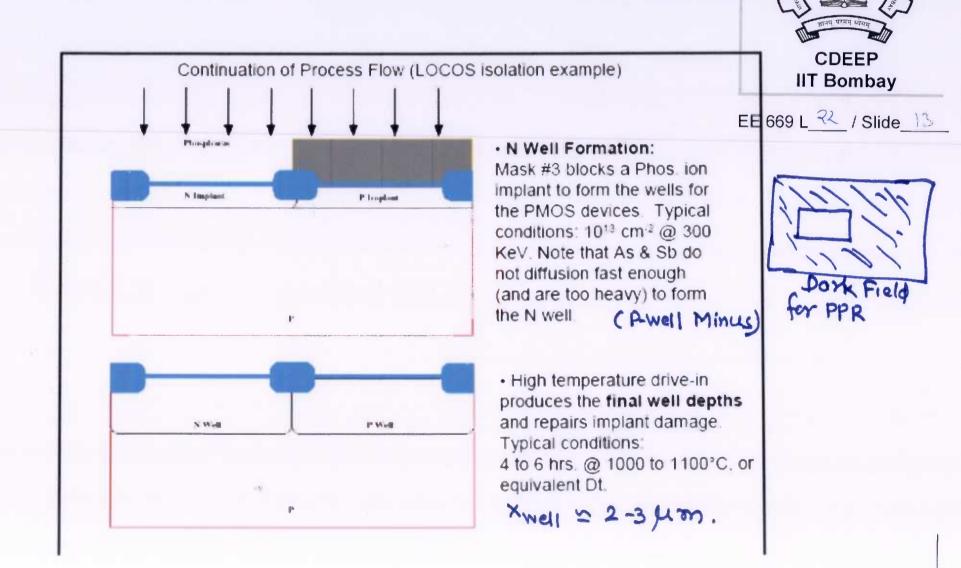

### Final N-Well and P-Well Creation

$$V_T = \phi_{ms} \pm 2\phi_F - \frac{Q_{ox}}{C_{ox}} \pm \frac{Q_B}{C_{ox}}$$

$$C_{ox} = \frac{C_{ox}}{t_{ox}} \rightarrow C_{aete} \text{ oxide Thickness}$$

EE 669 L 22 / Slide 14

Threshold Vy can be adjusted through 'QB'

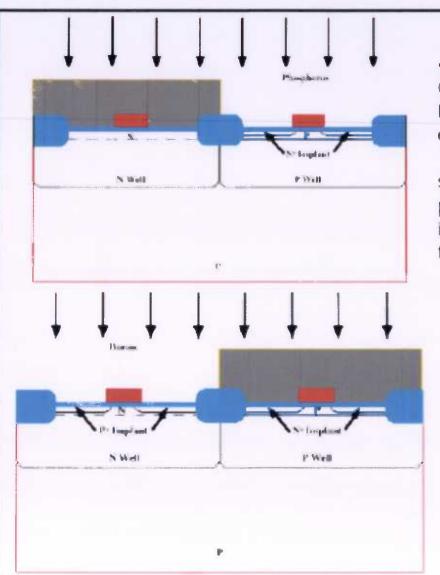

## **Threshold Adjust Implants**

Pikali

CDEEP IIT Bombay

EE 669 L 23 / Slide 5

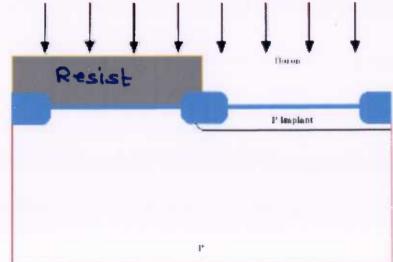

• NMOS  $V_{TH}$  adjust: Mask #4 is use to protect the PMOS devices. B is ion implanted to adjust  $V_{TH}$ . Typical conditions: 1-5 x  $10^{12}$  cm<sup>-2</sup>, 50 - 85 KeV.

• PMOS V<sub>TH</sub> adjust: Mask #5 is use to protect the NMOS devices. As is ion implanted to adjust V<sub>TH</sub>. Typical conditions: 1-5 x 10<sup>12</sup> cm<sup>-2</sup>, 75 - 100 KeV.

Mask 4 & Mask 5 are complimentary

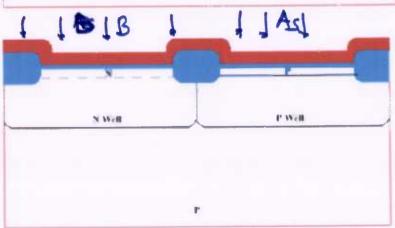

# Polysilicon Gate Realization

**CDEEP IIT Bombay**

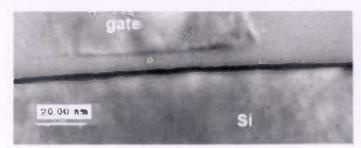

**Gate Stack Formation**

P Wall N Well

EE 669 L 2 / Slide 6 · Etch back thin oxide and grow clean gate oxide ~ 5 nm, which can be grown at 800°C in ~ 1 hr.

Nitrided oxides are typical today. and alternative high-K dielectrics are also being considered for Sub 90 nm, Node

LPCVD polysilicon gate deposition (~0.1 microns). Fither masked or unmasked polysilicon doping implant is then performed (target dose such that final average poly doping is  $> 10^{20} \text{ cm}^{-3}$ ).

Rs 10-20 ohm/1

Dry Oxidation

Doping of Poly! Iln Situ duriup Poly deposition 2 Solidstate Diff. 3. Implant

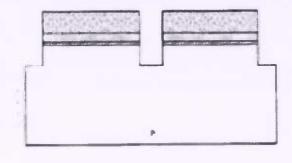

#### **Gate Delineation**

Gate etch: Mask #6 is used to protect the MOS gates. The polysilicon is plasma etched using an anisotropic etch which stops on the underlying oxide.

Process option: gate re-oxidation (to improve reliability in very thin gate oxide devices). Must be done carefully to avoid formation of non-uniform gate oxide thickness:

K. Rim, Ph.D. thesis, Stanford Univ.

EE 669 L 22 / Slide 17

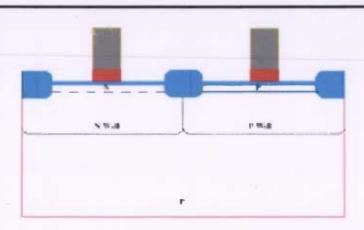

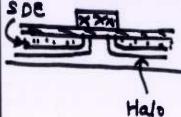

S/D Extensions for SCE reduction

NMOS S/D Extension formation:

Original concept was Lightly Doped

Drain (LDD) to help deal with hot

electron effects. Today, the S/D

extension serves to mitigate

short channel effects. Mask #7

protects the PMOS devices. An As+

implant forms the LDD regions in

the NMOS devices.

PMOS S/D Extension formation:

Mask #8 protects the PMOS devices.

A B+ implant forms the LDD or extension regions.

CDEEP IIT Bombay

EE 669 L 22 / Slide 18

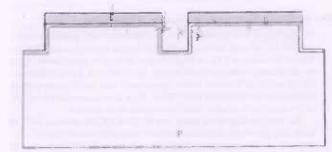

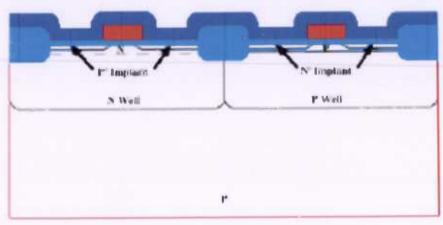

# Sidewall Spacer creation

P (mplant N forgilant N Well P Well

• Sidewall spacer formation (oxide):

A conformal layer of  $SiO_2$  is EE 669 L 22 / Slide 19deposited (typically ~ 0.1 to 0.25

microns thick) LPCVD Process.  $SiH_4 + O_2 \rightarrow SiO_2 + 2H_2$   $SiH_4 Cl_2 + N_2O \rightarrow SiO_2 + 2N_2 + 2H_2$

#### · Sidewall formation:

Anisotropic etching leaves behind "sidewall spacers" along the sides of the polysilicon gates.