| |

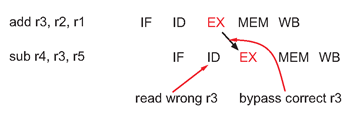

Data hazards

- Data dependency in instruction stream limits ILP

- True dependency (Read After Write: RAW)

- Need a bypass network to avoid losing cycles

- Without the bypass the fetching of subtraction would have to be delayed by three cycles

- This is an example of RAW hazard

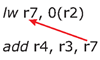

More on RAW

- The most problematic dependencies involve memory ops

- The memory ops may take a large number of cycles to return the value (if missed in cache)

- This type of dependencies is the primary cause of increase in CPI and lower ILP

Multi-cycle EX stage

- Thus far we have assumed a single cycle EX

- Consider multiplication and division

- Assume a four-cycle multiplication unit: mult r5, r4, r3 IF ID EX1 EX2 EX3 EX4 MEM WB

- Normally the multiplier is separate

- So the next instruction can start executing when mult moves to EX2 stage and, in fact, can finish before mult

|

| |

| |

| |

| |

| |

| |

| |

| |

| |

| |

| |

| |

| |

| |

|

|

|

|