| |

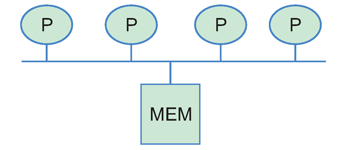

Shared memory MPs

- What is the communication protocol?

- Could be bus-based

- Processors share a bus and snoop every transaction on the bus

- The most common design in server and enterprise market

Bus-based MPs

- The memory is “equidistant” from all processors

- Normally called symmetric multiprocessors (SMPs)

- Fast processors can easily saturate the bus

- Bus bandwidth becomes a scalability bottleneck

- In `90s when processors were slow 32P SMPs could be seen

- Now mostly Sun pushes for large-scale SMPs with advanced bus architecture/technology

- The bus speed and width have also increased dramatically: Intel Pentium 4 boxes normally come with 400 MHz front-side bus, Xeons have 533 MHz or 800 MHz FSB, PowerPC G5 can clock the bus up to 1.25 GHz

Scaling: DSMs

- Large-scale shared memory MPs are normally built over a scalable switch-based network

- Now each node has its local memory

- Access to remote memory happens through load/store, but may take longer

- Non-Uniform Memory Access (NUMA)

- Distributed Shared Memory (DSM)

- The underlying coherence protocol is quite different compared to a bus-based SMP

- Need specialized memory controller to handle coherence requests and a router to connect to the network

|

| |

| |

| |

| |

| |

| |

| |

| |

| |

| |

| |

| |

| |

| |

|

|

|

|