| |

Pipelining:

- One simple observation

- Exactly one piece of hardware is active at any point in time

- Why not fetch a new instruction every cycle?

- Five instructions in five different phases

- Throughput increases five times (ideally)

- Bottom-line is

- If consecutive instructions are independent, they can be processed in parallel

- The first form of instruction-level parallelism (ILP)

Pipelining Hazards:

- Instruction dependence limits achievable parallelism

- Control and data dependence (aka hazards)

- Finite amount of hardware limits achievable parallelism

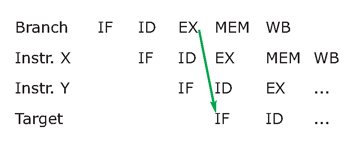

- Control dependence

- On average, every fifth instruction is a branch (coming from if-else, for, do-while,…)

- Branches execute in the third phase

- Introduces bubbles unless you are smart

Control Dependence:

What do you fetch in X and y slots?

Options: nothing, fall-through, learn past history and predict (today best predictors achieve on average 97% accuracy for SPEC2000) |